RL78/F13, F14 CHAPTER 15 SERIAL ARRAY UNIT

R01UH0368EJ0210 Rev.2.10 852

Dec 10, 2015

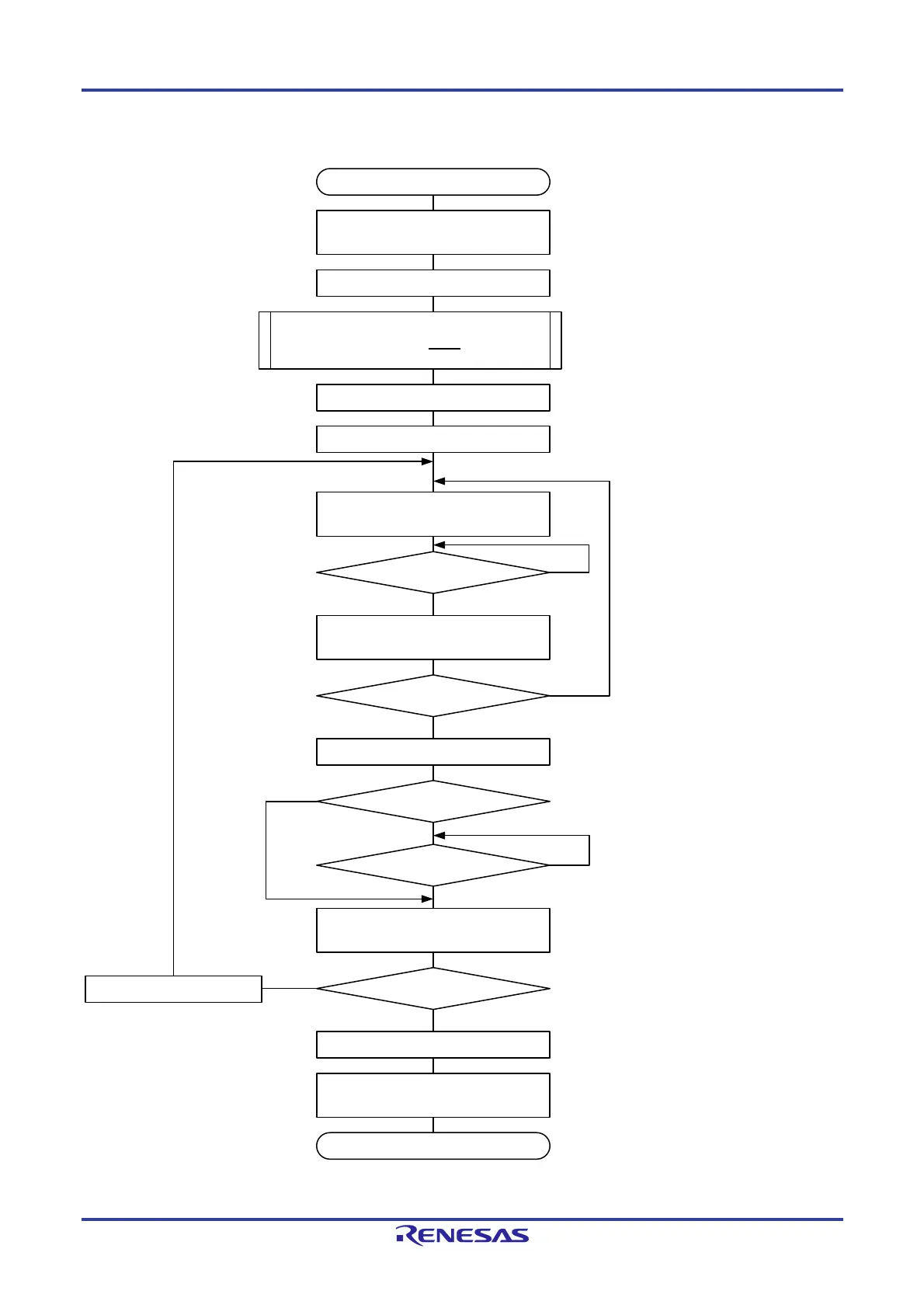

Figure 15-40. Flowchart of Master Reception (in Continuous Reception Mode)

(Caution and Remarks are listed on the next page.)

Starting CSI communication

Port manipulation

Setting the SAU1EN and

SAU0EN bits of the PER0 register to 1

Setting operation clock with

the SPSm register

No

Buffer empty interrupt generated?

Writing 1 to the SSmn bit

Writing dummy data to

the SDRmn register

Reading receive data from

the SDRmn register

Setting the SAU1EN and SAU0EN bits

of the PER0 register to 0

End of communication

Yes

<2>

Is the next receive data

the last one?

TSFmn = 1?

Transfer end interrupt generated?

Reading receive data from

the SDRmn register

No

No

Yes

No

Writing 1 to the MDmn0 bit

Yes

Specify the initial settings while the SEmn bit is

0.

<1> Select the buffer empty interrupt.

SMRmn, SCRmn: Setting communication

SDRmn[15:9]: Setting transfer rate

SOm: Setting SCKp output

Writing 0 to the MDmn0 bit

Reception continued?

Writing 1 to the STmn bit

No

<3>

<4>

Yes

<5>

<6>

<7>

<8>

Yes

Loading...

Loading...