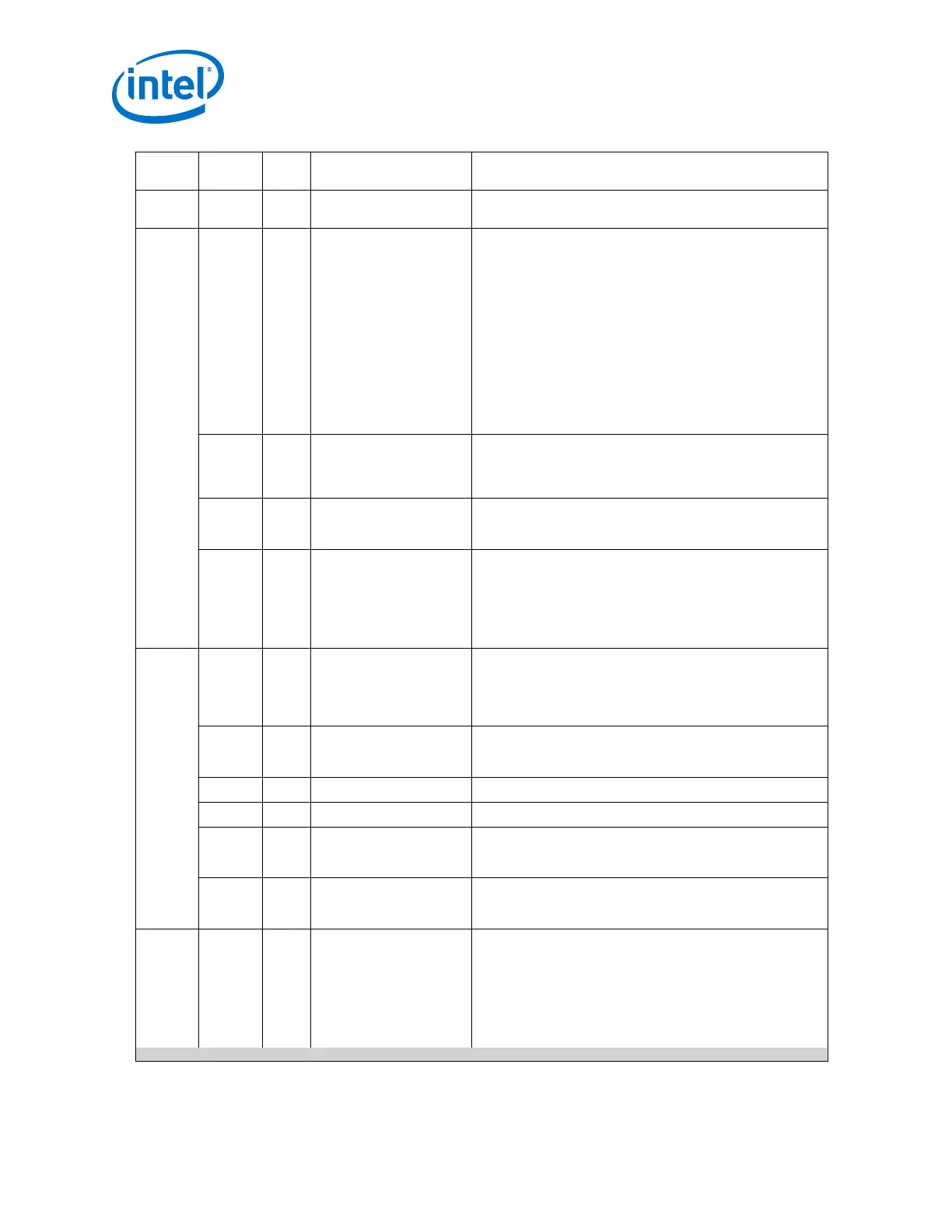

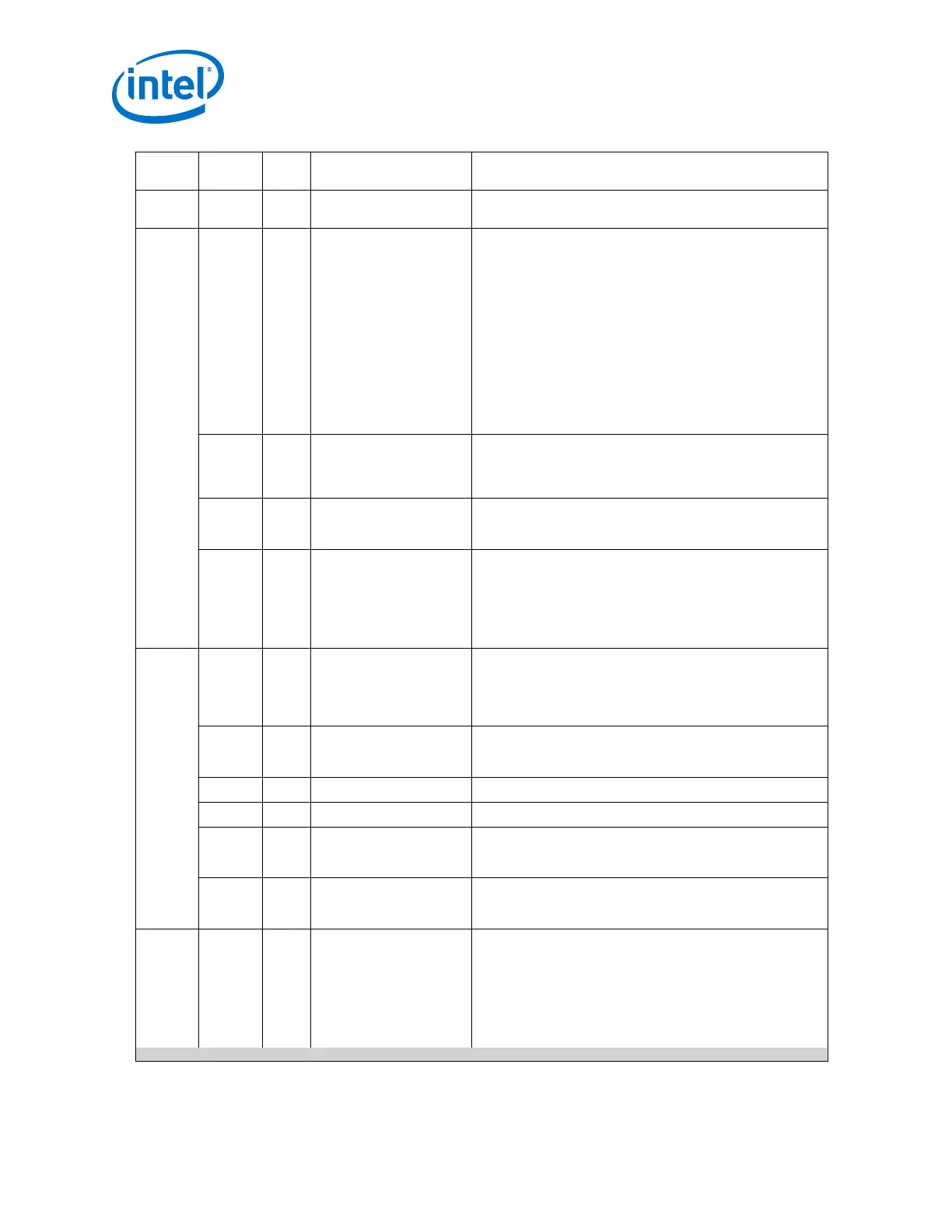

Word

Addr

Bit R/W Name Description

0x4CA 31:0 RO

LP Next page high

The AN RX state machine receives these bits from the link

partner. Bits [31:0] correspond to page bits [47:16]

0x4CB 24:0 RO

AN LP ADV

Tech_A[24:0]

Received technology ability field bits of Clause 73 Auto

Negotiation. The 10GBASE-KR PHY supports A0 and A2. The

following protocols are defined:

• A0 1000BASE-KX

• A1 10GBASE-KX4

• A2 10GBASE-KR

• A3 40GBASE-KR4

• A4 40GBASE-CR4

• A5 100GBASE-CR10

• A24:6 are reserved

For more information, refer to Clause 73.6.4 and AN LP base

page ability registers (7.19-7.21) of Clause 45 of IEEE

802.3ap-2007.

26:25 RO

AN LP ADV FEC_F[1:0]

Received FEC ability bits FEC (F0:F1) is encoded in bits

D46:D47 of the base Link Codeword. F0 is FEC ability. F1 is

FEC requested. See Clause 73.6.5 of IEEE 802.3ap-2007 for

details.

27 RO

AN LP ADV Remote

Fault

Received Remote Fault (RF) ability bits. RF is encoded in bit

D13 of the base link codeword in Clause 73 AN. For more

information, refer to Clause 73.6.7 of IEEE 802.3ap-2007.

30:28 RO

AN LP ADV Pause

Ability_C[2:0]

Received pause ability bits. Pause (C0:C1) is encoded in bits

D11:D10 of the base link codeword in Clause 73 AN as

follows:

• C0 is the same as PAUSE as defined in Annex 28B

• C1 is the same as ASM_DIR as defined in Annex 28B

• C2 is reserved

0x4D0 0 RW

Link Training enable

When 1, enables the 10GBASE-KR start-up protocol. When 0,

disables the 10GBASE-KR start-up protocol. The default value

is 1. For more information, refer to Clause 72.6.10.3.1 and

10GBASE-KR PMD control register bit (1.150.1) of IEEE

802.3ap-2007.

1 RW

dis_max_wait_tmr When set to 1, disables the LT max_wait_timer. Used for

characterization mode when setting much longer BER timer

values. The default value is 0.

2 RW Reserved Reserved

3 RW Reserved Reserved

7:4 RW

main_step_cnt [3:0]

Specifies the number of equalization steps for each main tap

update. There are about 20 settings for the internal algorithm

to test. The valid range is 1-15. The default value is 4'b0001.

11:8 RW

prepost_step_cnt

[3:0]

Specifies the number of equalization steps for each pre- and

post-tap update. From 16-31 steps are possible. The default

value is 4'b0001.

0x4D0 14:12 RW

equal_cnt [2:0]

Adds hysteresis to the error count to avoid local minimums.

The following values are defined:

• 000 = 0

• 001 = 2

• 010 = 4

• 011 = 8

• 100 = 16

continued...

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

154

Loading...

Loading...