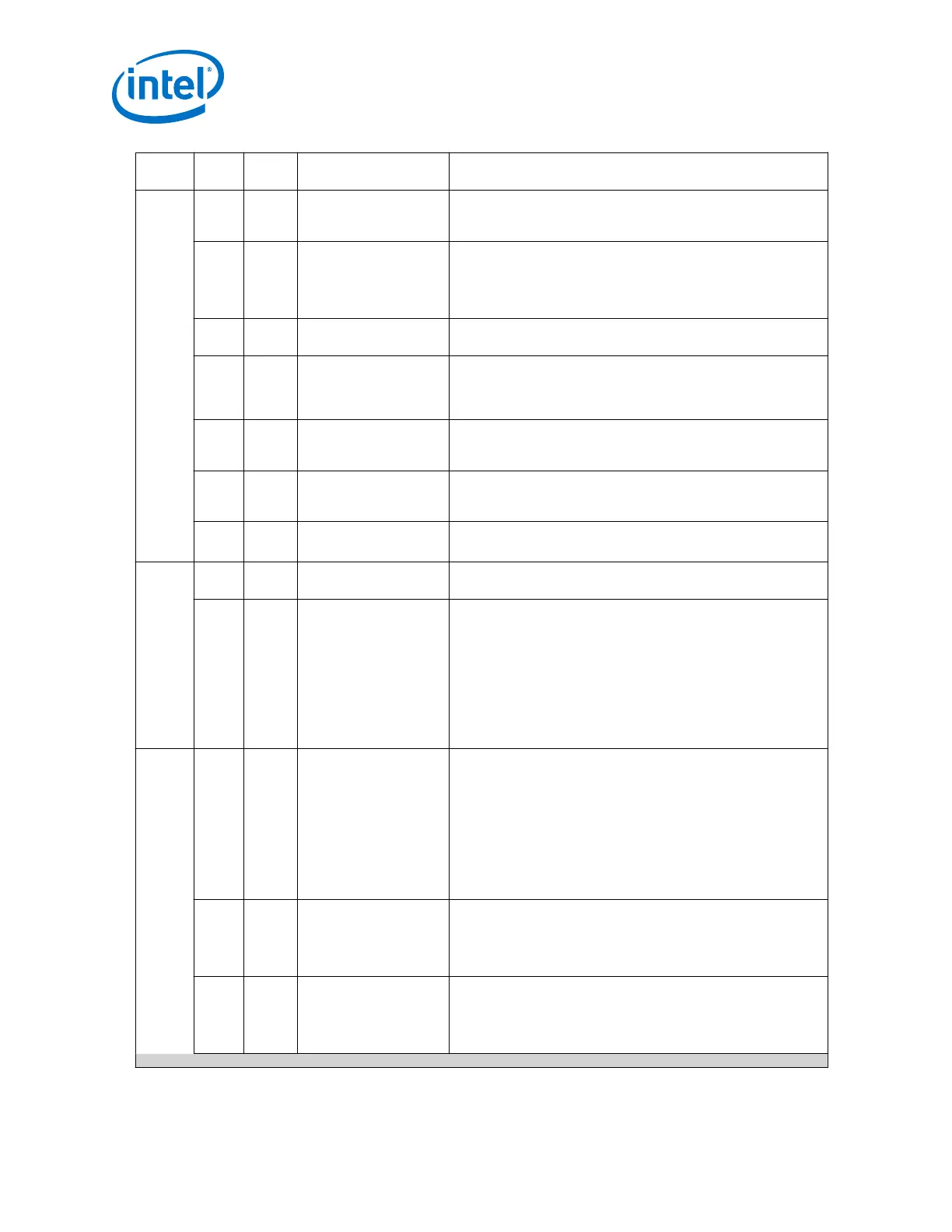

Word

Addr

Bit R/W Name Description

2 RO

AN Complete

When asserted, AN has completed. When 0, AN is in progress. For

more information, refer to bit 7.1.5 in Clause 73.8 of IEEE

802.3ap-2007.

3 RO

AN ADV Remote Fault

When set to 1, fault information has been sent to the link partner.

When 0, a fault has not occurred. The current value clears when

the register is read. Remote Fault (RF) is encoded in bit D13 of

the base Link Codeword. For more information, refer to Clause

73.6.7 of and bit 7.16.13 of IEEE 802.3ap-2007.

4 RO

AN RX SM Idle

When set to 1, the AN state machine is in the idle state. Incoming

data is not Clause 73 compatible. When 0, the AN is in progress.

5 RO

AN Ability

When set to 1, the transceiver PHY is able to perform AN. When

set to 0, the transceiver PHY is not able to perform AN. If your

variant includes AN, this bit is tied to 1. For more information,

refer to bits 7.1.3 and 7.48.0 of Clause 45 of IEEE 802.3ap-2007.

6 RO

AN Status

When set to 1, link is up. When 0, the link is down. The current

value clears when the register is read. For more information, refer

to bit 7.1.2 of Clause 45 of IEEE 802.3ap-2007.

7 RO

LP AN Ability

When set to 1, the link partner is able to perform AN. When 0,

the link partner is not able to perform AN. For more information,

refer to bit 7.1.0 of Clause 45 of IEEE 802.3ap-2007.

8 RO

FEC negotiated –

enable FEC from SEQ

When set to 1, the PHY is negotiated to perform FEC. When set to

0, the PHY is not negotiated to perform FEC.

0x4C2 9 RO

Seq AN Failure

When set to 1, a sequencer AN failure has been detected. When

set to 0, an AN failure has not been detected.

17:12 RO

KR AN Link

Ready[5:0]

Provides a one-hot encoding of an_receive_idle = true and

link status for the supported link as described in Clause 73.10.1.

The following encodings are defined:

• 6'b000000: 1000BASE-KX

• 6'b000001: 10GBASE-KX4

• 6'b000100: 10GBASE-KR

• 6'b001000: 40GBASE-KR4

• 6'b010000: 40GBASE-CR4

• 6'b100000: 100GBASE-CR10

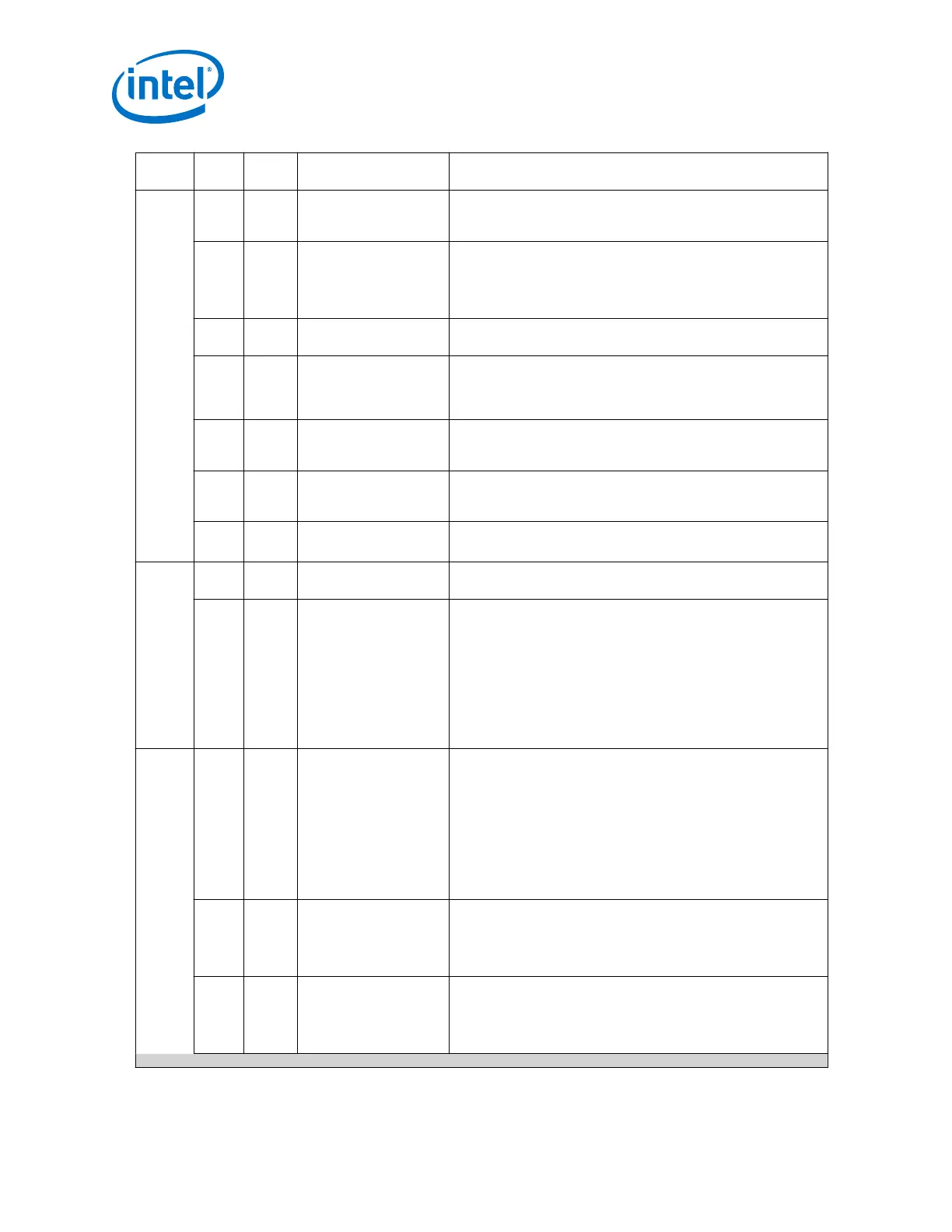

0x4C3

15:0 RW

User base page low

The AN TX state machine uses these bits if the AN base pages ctrl

bit is set. The following bits are defined:

• [15]: Next page bit

• [14]: ACK, controlled by the SM

• [13]: Remote Fault bit

• [12:10]: Pause bits

• [9:5]: Echoed nonce, set by the state machine

• [4:0]: Selector

The auto generation TX state machine generates the PRBS bit 49.

21:16 RW

Override

AN_TECH[5:0]

AN_TECH value to override. The following bits are defined:

•

Bit-16 = AN_TECH[0]= 1000BASE-KX

•

Bit-18 = AN_TECH[2] = 10GBASE-KR

You must set 0xC0 bit-5 for this to take effect .

25:24 RW

Override

AN_FEC[1:0]

AN_FEC value to override. The following bits are defined:

•

Bit-24 = AN_FEC [0] = Capability

•

Bit-25 = AN_FEC [1] = Request

You must set 0xC0 bit-5 for this to take effect.

continued...

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

184

Loading...

Loading...