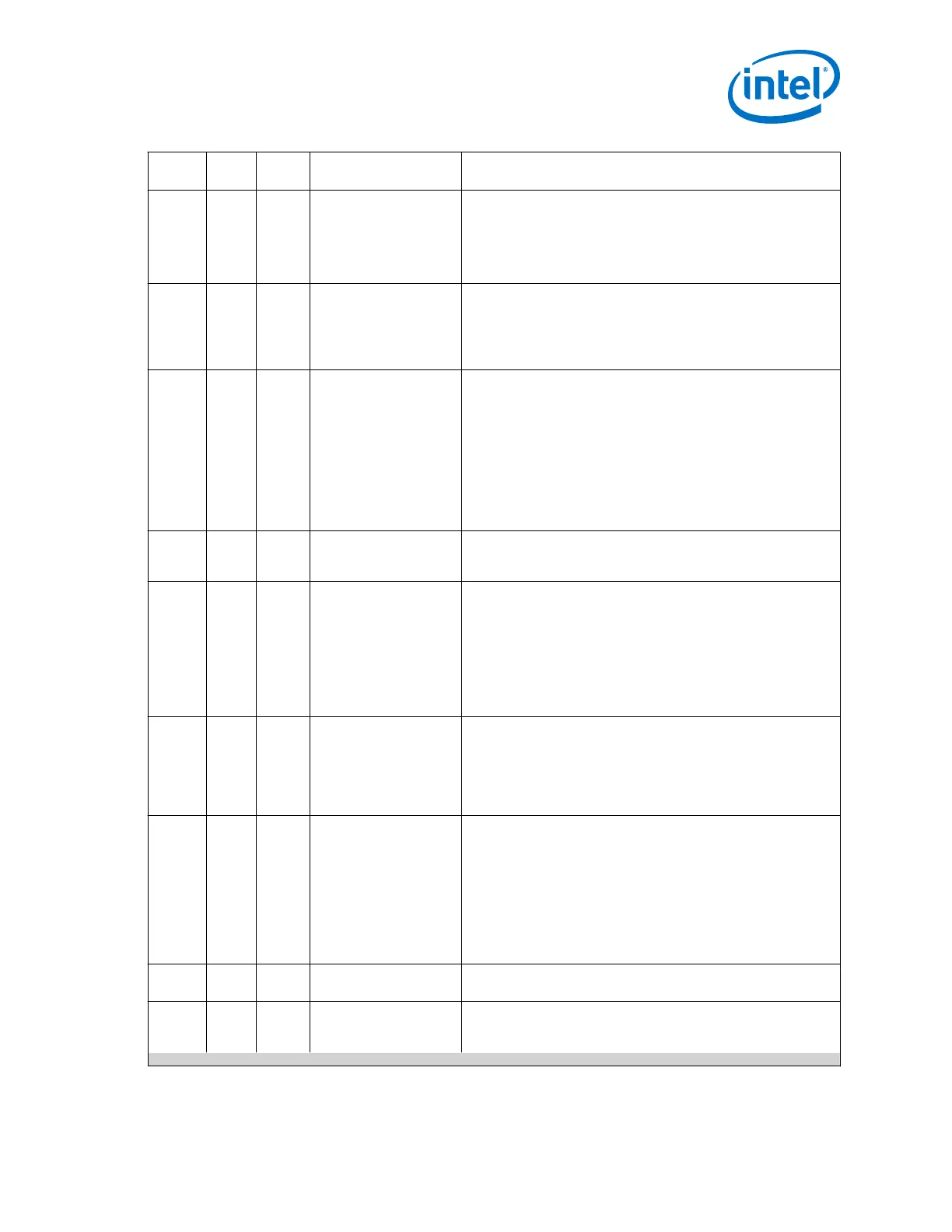

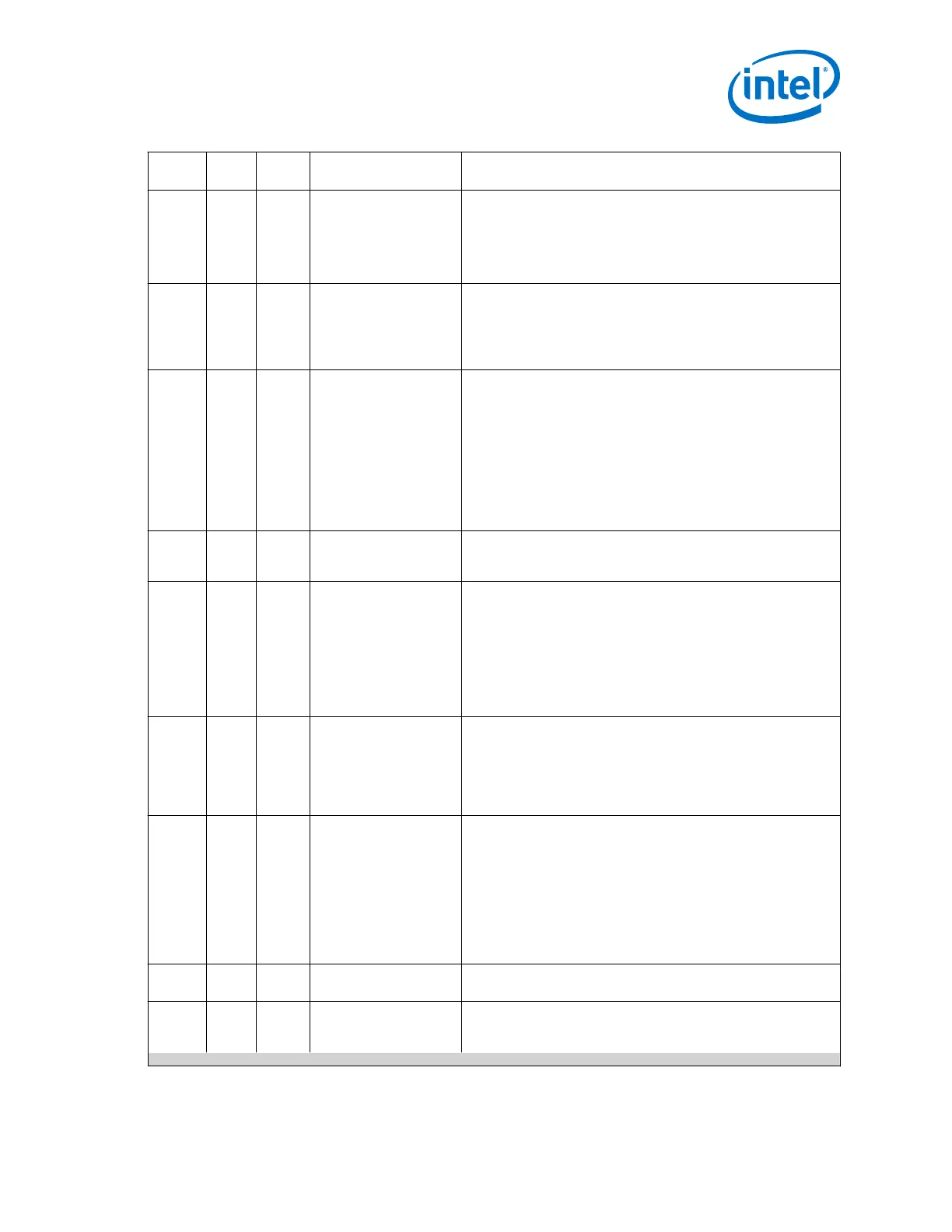

Word

Addr

Bit R/W Name Description

30:28 RW

Override

AN_PAUSE[2:0]

AN_PAUSE value to override. The following bits are defined:

•

Bit-28 = AN_PAUSE [0] = Pause Ability

•

Bit-29 = AN_PAUSE [1] = Asymmetric Direction

•

Bit-30 = AN_PAUSE [2] = Reserved

You must set 0xC0 bit-5 for this to take effect.

0x4C4 31:0 RW

User base page high

The AN TX state machine uses these bits if the AN base pages ctrl

bit is set. The following bits are defined:

• [29:5]: Correspond to page bits 45:21, the technology ability.

• [4:0]: Correspond to bits 20:16, the TX nonce bits.

The AN TX state machine generates the PRBS bit 49.

0x4C5 15:0 RW

User Next page low

The AN TX state machine uses these bits if the AN next pages ctrl

bit is set. The following bits are defined:

• [15]: Next page bit

• [14]: ACK, controlled by the state machine

• [13]: Message Page (MP) bit

• [12]: ACK2 bit

• [11]: Toggle bit

For more information, refer to Clause 73.7.7.1 Next Page

encodings of IEEE 802.3ap-2007. Bit 49, the PRBS bit, is

generated by the AN TX state machine.

0x4C6 31:0 RW

User Next page high

The AN TX state machine uses these bits if the AN next pages ctrl

bit is set. Bits [31:0] correspond to page bits [47:16]. Bit 49, the

PRBS bit, is generated by the AN TX state machine.

0x4C7 15:0 RO

LP base page low

The AN RX state machine receives these bits from the link

partner. The following bits are defined:

• [15] Next page bit

• [14] ACK, which is controlled by the state machine

• [13] RF bit

• [12:10] Pause bits

• [9:5] Echoed nonce which are set by the state machine

• [4:0] Selector

0x4C8 31:0 RO

LP base page high

The AN RX state machine received these bits from the link

partner. The following bits are defined:

• [31:30]: Reserved

• [29:5]: Correspond to page bits [45:21], the technology

ability

• [4:0]: Correspond to bits [20:16], the TX Nonce bits

0x4C9 15:0 RO

LP Next page low

The AN RX state machine receives these bits from the link

partner. The following bits are defined:

• [15]: Next page bit

• [14]: ACK which is controlled by the state machine

• [13]: MP bit

• [12] ACK2 bit

• [11] Toggle bit

For more information, refer to Clause 73.7.7.1 Next Page

encodings of IEEE 802.3ap-2007.

0x4CA 31:0 RO

LP Next page high

The AN RX state machine receives these bits from the link

partner. Bits [31:0] correspond to page bits [47:16].

0x4CB 24:0 RO

AN LP ADV

Tech_A[24:0]

Received technology ability field bits of Clause 73 Auto-

Negotiation. The 10GBASE-KR PHY supports A0 and A2. The

following protocols are defined:

continued...

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

185

Loading...

Loading...