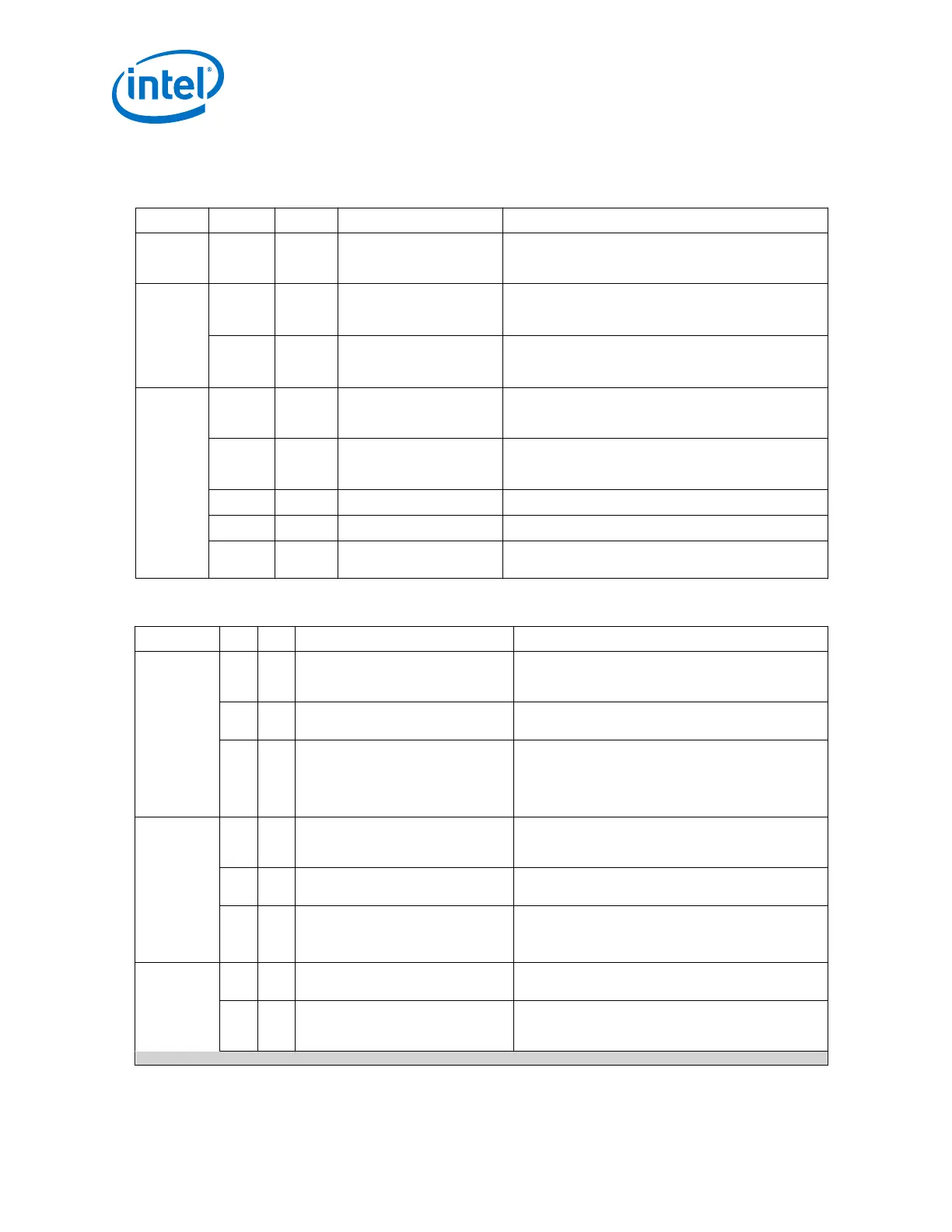

2.6.4.7.3. Enhanced PCS Registers

Table 147. Enhanced PCS Registers

Addr Bit Access Name Description

0x480 31:0 RW

Indirect_addr

Because the PHY implements a single channel, this

register must remain at the default value of 0 to specify

logical channel 0.

0x481 2 RW

RCLR_ERRBLK_CNT

Error block counter clear register. When set to 1, clears

the RCLR_ERRBLK_CNT register. When set to 0, normal

operation continues.

3 RW

RCLR_BER_COUNT

BER counter clear register. When set to 1, clears the

RCLR_BER_COUNT register. When set to 0, normal

operation continues.

0x482 1 RO

HI_BER

High BER status. When set to 1, the PCS reports a high

BER. When set to 0, the PCS does not report a high

BER.

2 RO

BLOCK_LOCK

Block lock status. When set to 1, the PCS is locked to

received blocks. When set to 0, the PCS is not locked to

received blocks.

3 RO

TX_FIFO_FULL When set to 1, the TX_FIFO is full.

4 RO

RX_FIFO_FULL When set to 1, the RX_FIFO is full.

7 RO

Rx_DATA_READY

When set to 1, indicates the PHY is ready to receive

data.

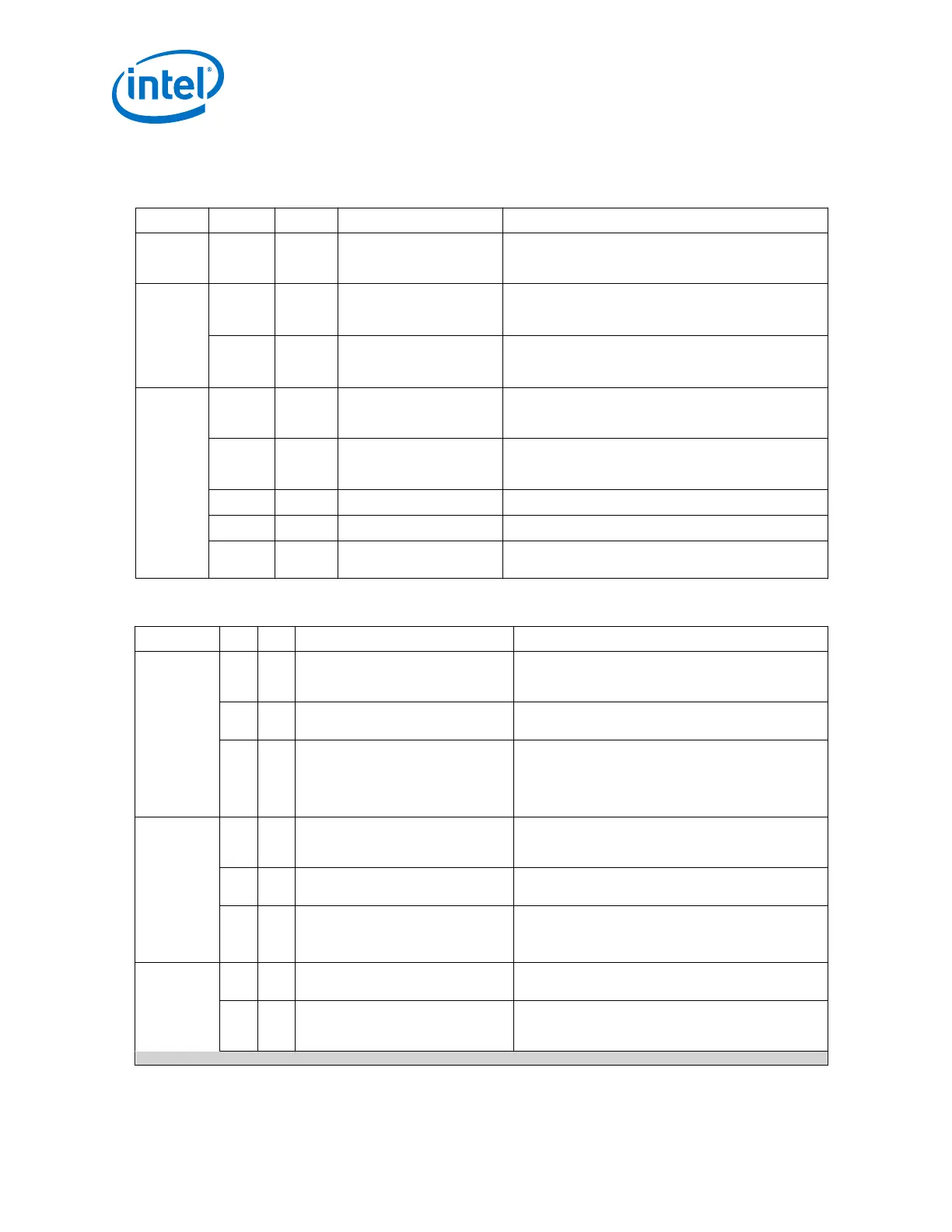

2.6.4.7.4. Arria 10 GMII PCS Registers

Addr

Bit R/W Name Description

0x490 9 RW

RESTART_AUTO_ NEGOTIATION

Set this bit to 1 to restart the Clause 37 auto-

negotiation (AN) sequence. For normal operation, set

this bit to the default 0 value. This bit is self-clearing.

12 RW

AUTO_NEGOTIATION_ ENABLE

Set this bit to 1 to enable Clause 37 AN. The default

value is 1.

15 RW

Reset

Set this bit to 1 to generate a synchronous reset pulse

which resets all the PCS state machines, comma

detection function, and the 8B/10B encoder and

decoder. For normal operation, set this bit to 0. This

bit self clears.

0x491 2 R

LINK_STATUS

A value of 1 indicates that a valid link is operating. A

value of 0 indicates an invalid link. If link

synchronization is lost, this bit is 0.

3 R

AUTO_NEGOTIATION_ ABILITY

A value of 1 indicates that the PCS function supports

Clause 37 AN.

5 R

AUTO_NEGOTIATION_ COMPLETE

A value of 1 indicates the following status:

• The AN process is complete.

• The AN control registers are valid.

0x494

(1000BASE-

X mode)

5 RW

FD

Full-duplex mode enable for the local device. Set to 1

for full-duplex support.

6 RW

HD

Half-duplex mode enable for the local device. Set to 1

for half-duplex support. This bit should always be set

to 0 for the KR PHY IP.

continued...

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

192

Loading...

Loading...