Word

Addr

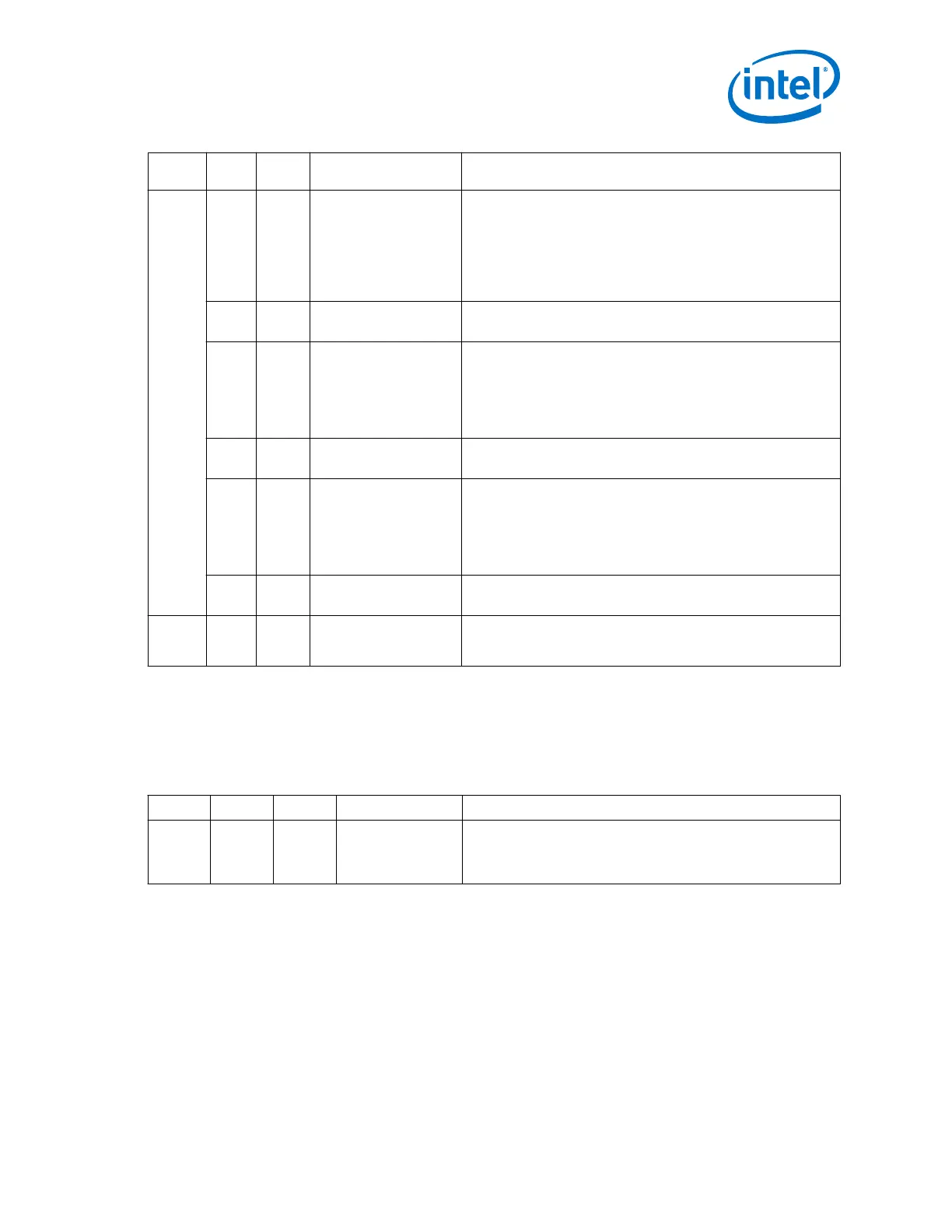

Bit R/W Name Description

12:8 RW

LT VODMin ovrd Override value for the VODMINRULE parameter. When enabled,

this value substitutes for the VMINRULE to allow channel-by-

channel override of the device settings. This override only effects

the local device TX output for this channel.

The value to be substituted must be less than the INITMAINVAL

parameter and greater than the VMINRULE parameter for proper

operation.

13 RW

LT VODMin ovrd

Enable

When set to 1, enables the override value for the VODMINRULE

parameter stored in the LT VODMin ovrd register field.

21:16 RW

LT VPOST ovrd Override value for the VPOSTRULE parameter. When enabled, this

value substitutes for the VPOSTRULE to allow channel-by-channel

override of the device settings. This override only effects the local

device TX output for this channel.

The value to be substituted must be greater than the

INITPOSTVAL parameter for proper operation.

22 RW

LT VPOST ovrd

Enable

When set to 1, enables the override value for the VPOSTRULE

parameter stored in the LT VPOST ovrd register field.

28:24 RW

LT VPre ovrd Override value for the VPRERULE parameter. When enabled, this

value substitutes for the VPOSTRULE to allow channel-by-channel

override of the device settings. This override only effects the local

device TX output for this channel.

The value greater than the INITPREVAL parameter for proper

operation.

29 RW

LT VPre ovrd Enable When set to 1, enables the override value for the VPRERULE

parameter stored in the LT VPre ovrd register field.

0x4D7

to

0x4FF

Reserved for 40G KR Left empty for address compatibility with 40G MAC+PHY KR

solution.

Related Information

Reconfiguration Interface and Dynamic Reconfiguration on page 502

2.6.4.7.2. Hard Transceiver PHY Registers

Table 146. Hard Transceiver PHY Registers

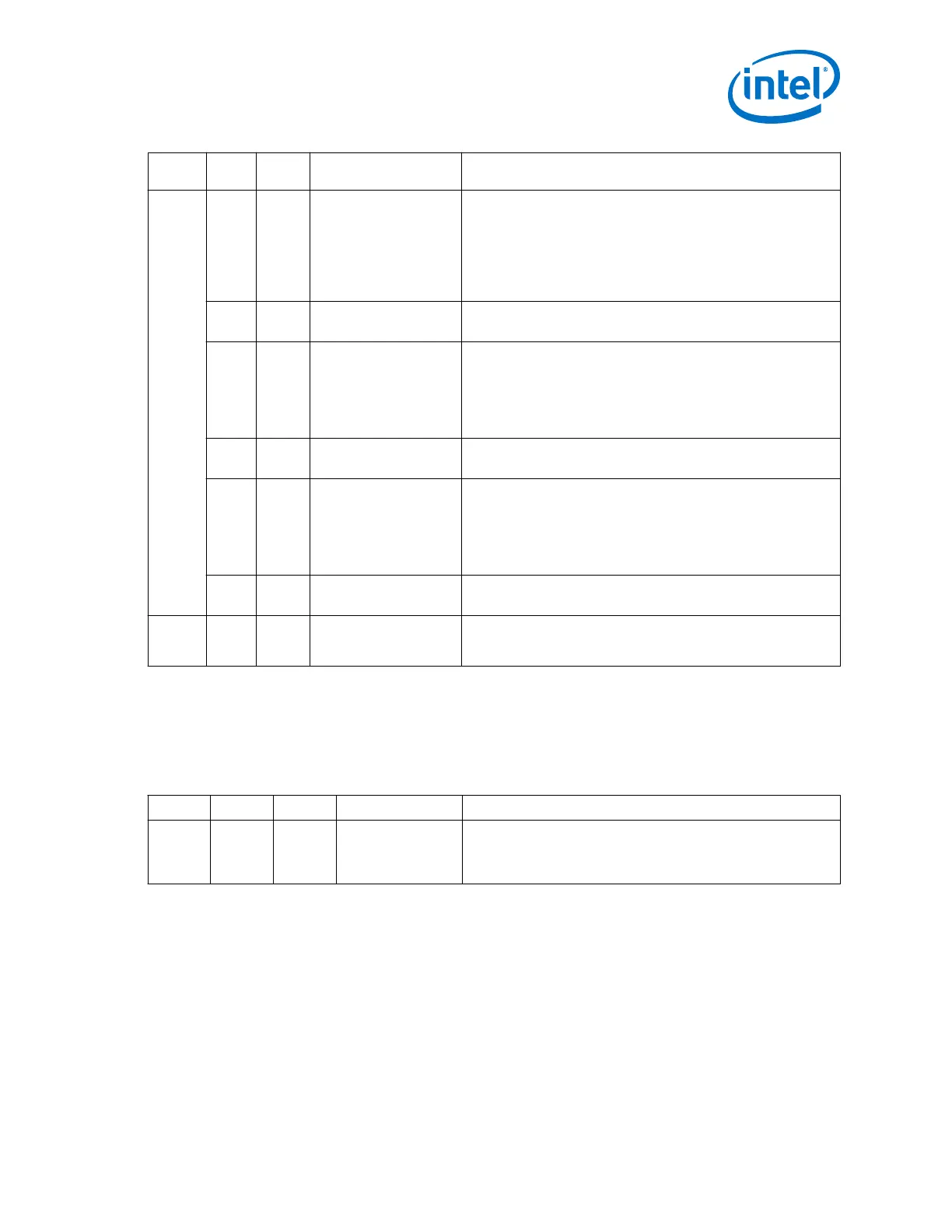

Addr Bit Access Name Description

0x000-0

x3FF

[9:0] RW Access to HSSI

registers

All registers in the physical coding sub-layer (PCS) and physical

media attachment (PMA) that you can dynamically reconfigure

are in this address space. Refer to the Arria 10 Dynamic

Transceiver Reconfiguration chapter for further information.

Related Information

Reconfiguration Interface and Dynamic Reconfiguration on page 502

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

191

Loading...

Loading...