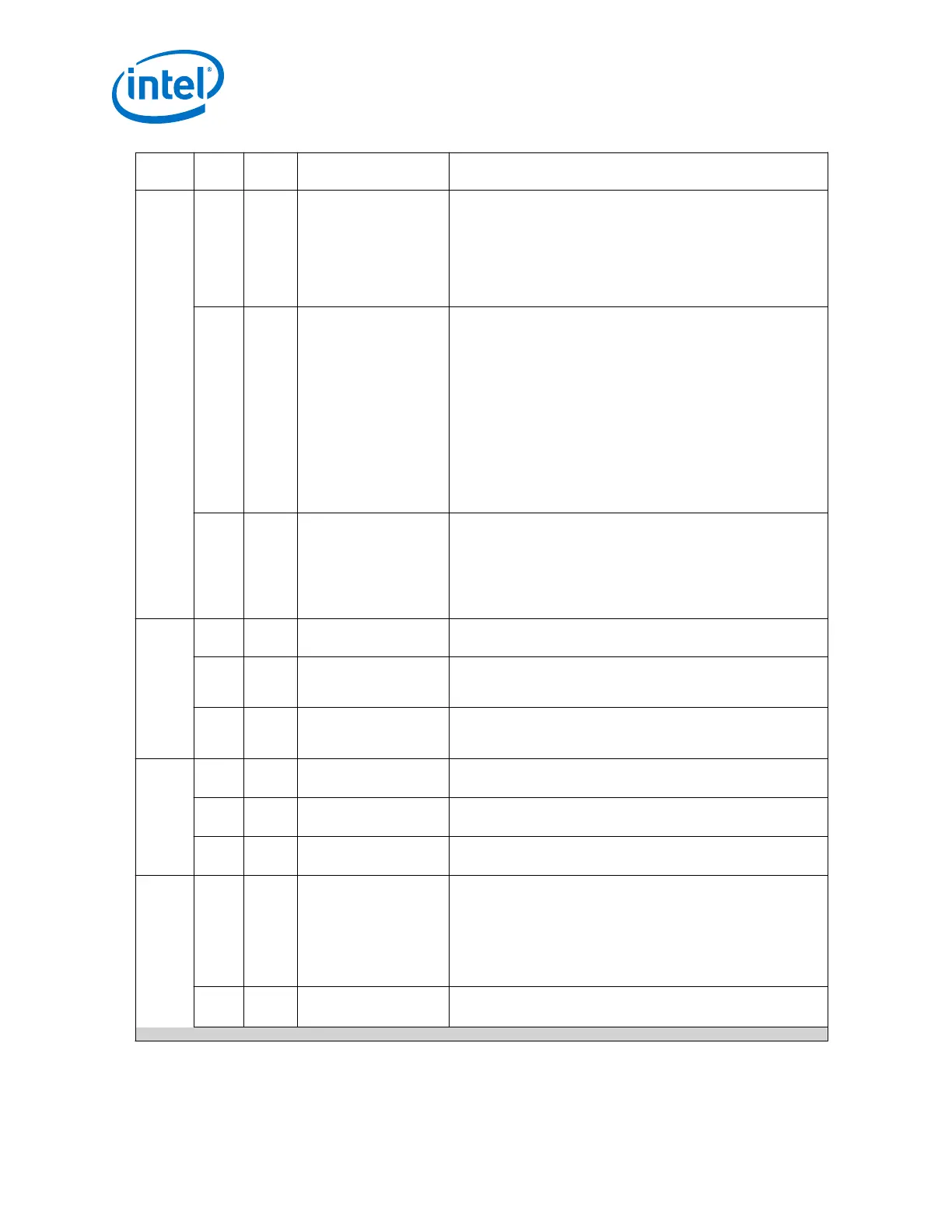

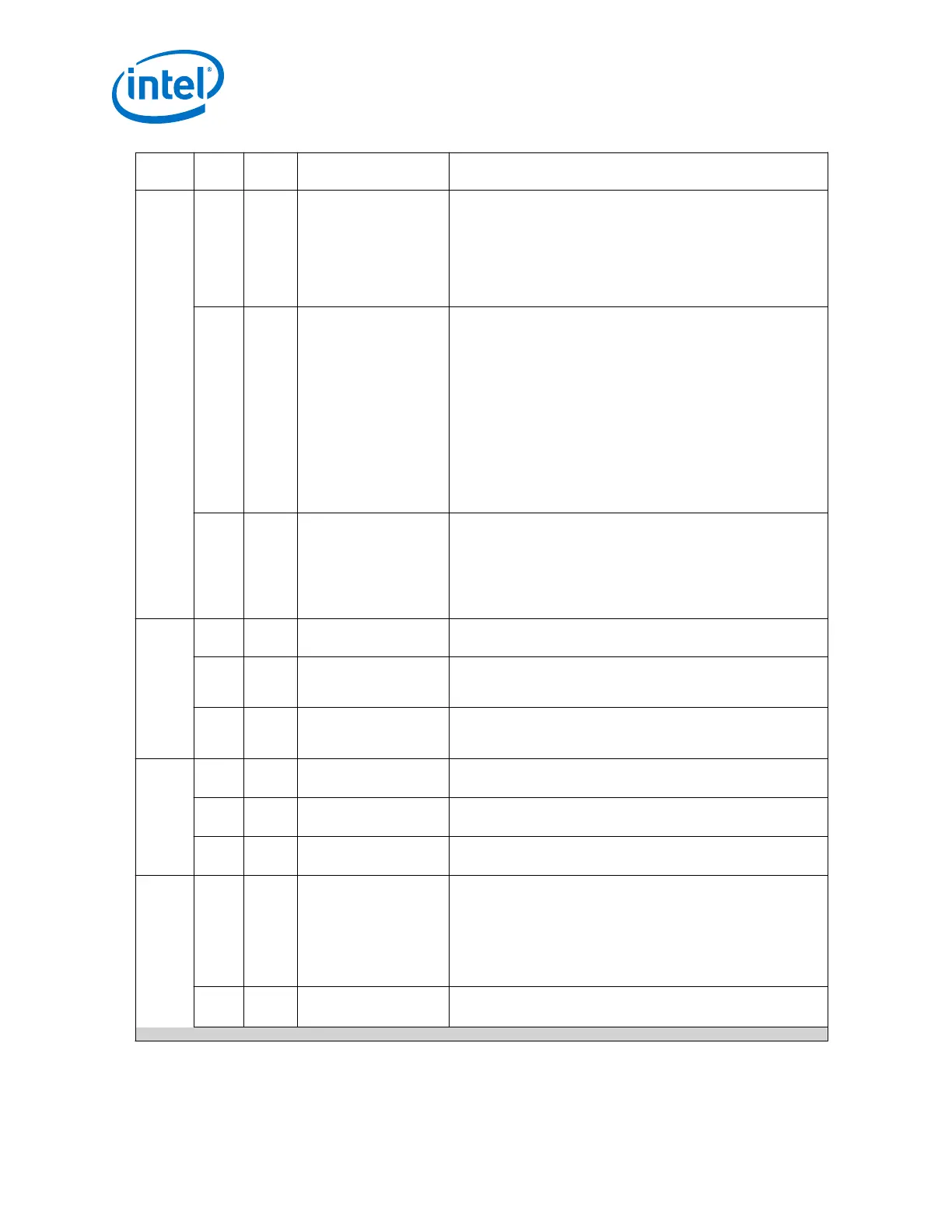

Word

Addr

Bit R/W Name Description

0x4D4 23 RO or

RW

LP Preset

Coefficients

When set to 1, the local device TX coefficients are set to a state

where equalization is turned off. Preset coefficients are used.

When set to 0, the local device operates normally. The function

and values of the preset bit are defined in 72.6.10.2.3.1. The

function and values of the initialize bit are defined in Clause

72.6.10.2.3.2. For more information, refer to bit 10GBASE-KR LP

coefficient update register bits (1.152.13) in Clause 45.2.1.78.3

of IEEE 802.3ap-2007.

29:24 RO

LP coefficient

status[5:0]

Status report register reflecting the contents of the second, 16-bit

word of the training frame most recently received from the

control channel. The following fields are defined:

• [5:4]: Coefficient (+1)

— 2'b11: Maximum

— 2'b01: Minimum

— 2'b10: Updated

— 2'b00: Not updated

• [3:2]: Coefficient (0) (same encoding as [5:4])

• n [1:0]: Coefficient (-1) (same encoding as [5:4])

For more information, refer to bit 10GBASE-KR LP status report

register bits (1.153.5:0) in Clause 45.2.1.79 of IEEE

802.3ap-2007.

30 RO

LP Receiver ready

When set to 1, the link partner receiver has determined that

training is complete and is prepared to receive data. When set to

0, the link partner receiver is requesting that training continue.

Values for the receiver ready bit are defined in Clause

72.6.10.2.4.4. For more information, refer to bit 10GBASE-KR LP

status report register bits (1.153.15) in Clause 45.2.1.79 of IEEE

802.3ap-2007.

0x4D5 4:0 R

LT V

OD

setting

Stores the most recent V

OD

setting that LT specified. It reflects

Link Partner commands to fine-tune the V

OD

.

13:8 R

LT Post-tap setting

Stores the most recent post-tap setting that LT specified. It

reflects Link Partner commands to fine-tune the TX pre-emphasis

taps.

20:16 R

LT Pre-tap setting

Stores the most recent pre-tap setting that LT specified. It

reflects Link Partner commands to fine-tune the TX pre-emphasis

taps.

0x4D5 27:24 R

RXEQ CTLE Setting Most recent ctle_rc setting sent to the reconfig bundle during

RX equalization.

29:28 R

RXEQ CTLE Mode Most recent ctle_mode setting sent to the reconfig bundle

during RX equalization.

31:30 R

RXEQ DFE Mode Most recent dfe_mode setting sent to the reconfig bundle during

RX equalization.

0x4D6 4:0 RW

LT VODMAX ovrd Override value for the VMAXRULE parameter. When enabled, this

value substitutes for the VMAXRULE to allow channel-by-channel

override of the device settings. This only effects the local device

TX output for the channel specified.

This value must be greater than the INITMAINVAL parameter for

proper operation. Note this also overrides the PREMAINVAL

parameter value.

5 RW

LT VODMAX ovrd

Enable

When set to 1, enables the override value for the VMAXRULE

parameter stored in the LT VODMAX ovrd register field.

continued...

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

190

Loading...

Loading...