The PIPE core provides a 1-bit PHY status signal pipe_phy_status and a 3-bit

receiver status signal pipe_rx_status[2:0] to indicate whether a receiver is

detected, as per the PIPE 2.0 specifications.

2.7.2.1.7. Gen1 and Gen2 Clock Compensation

In compliance with the PIPE specification, Arria 10 receiver channels have a rate

match FIFO to compensate for small clock frequency differences up to ±300 ppm

between the upstream transmitter and the local receiver clocks.

Consider the following guidelines for PIPE clock compensation:

• Insert or delete one SKP symbol in an SKP ordered set.

• Minimum limit is imposed on the number of SKP symbols in SKP ordered set after

deletion. An ordered set may have an empty COM case after deletion.

• Maximum limit is imposed on the number of the SKP symbols in the SKP ordered

set after insertion. An ordered set may have more than five symbols after

insertion.

• For INSERT/DELETE cases: The flag status appears on the COM symbol of the SKP

ordered set where insertion or deletion occurs.

• For FULL/EMPTY cases: The flag status appears where the character is inserted or

deleted.

Note: When the PIPE interface is on, it translates the value of the flag to the

appropriate pipe_rx_status signal.

• The PIPE mode also has a “0 ppm” configuration option that you can use in

synchronous systems. The Rate Match FIFO Block is not expected to do any clock

compensation in this configuration, but latency is minimized.

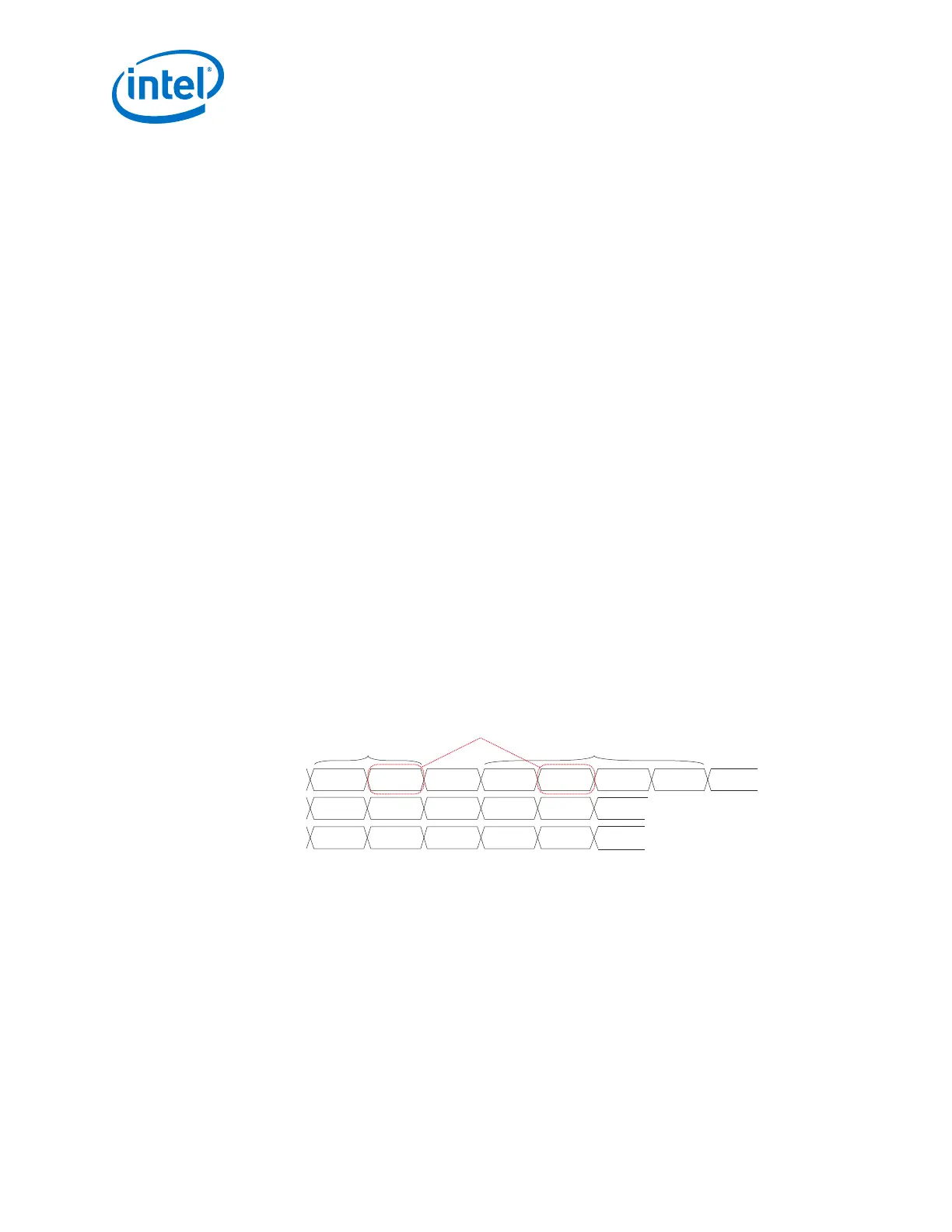

Figure 92. Rate Match Deletion

This figure shows an example of rate match deletion in the case where two /K28.0/ SKP symbols must be

deleted. Only one /K28.0/ SKP symbol is deleted per SKP ordered set received.

K28.5 K28.0 Dx.y K28.5 K28.0 K28.0 K28.0rmfifo_input_data

First SKP Ordered Set Second SKP Ordered Set

SKP Symbol

Deleted

K28.5 Dx.y K28.5 K28.0 K28.0rx_parallel_data

pipe_rx_status[2:0]

3’b010 xxx 3’b010 xxx xxx

Dx.y

Dx.y

xxx

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

234

Loading...

Loading...