The Root Port decodes these coefficients and presets, performs legality checks for

the three transmitter coefficient rules and applies the settings to its transmitter

and also sends them in the Training Sets. The default Full Swing (FS) value

advertised by the Intel device is 60 and Low Frequency (LF) is 20. The three rules

for transmitter coefficients are:

a. |C

-1

| <= Floor (FS/4)

b. |C

-1

|+C

0

+|C

+1

| = FS

c. C

0

-|C

-1

|-|C

+1

|>= LF

Where: C

0

is the main cursor (boost), C

-1

is the pre-cursor (pre-shoot), and C

+1

is

the post-cursor (de-emphasis).

3. This process is repeated until the downstream component's receiver achieves a

BER of < 10

-12

Phase 3 (Optional)

During this phase, the Root Port tunes the Endpoint’s transmitter. This process is

analogous to Phase 2 but operates in the opposite direction.

After Phase 3 tuning is complete, the Root Port moves to Recovery.RcvrLock, sending

EC=2’b00, and the final coefficients or preset agreed upon in Phase 2. The Endpoint

moves to Recovery.RcvrLock using the final coefficients or preset agreed upon in

Phase 3.

Recommendations for Tuning Link

To improve the BER of the receiver, Intel recommends that you turn on CTLE in

triggered mode during Phase 2 Equalization for Endpoints or Phase 3 Equalization for

Root Ports.

Use the port pipe_g3_txdeemph[17:0] to transmit the coefficients corresponding

to the Gen3 presets. Intel recommends transmitting Preset P8 coefficients for A10

receiver to recover data successfully. The pipe_g3_txdeemph is used to select the

link partner’s transmitter de-emphasis during equalization.

Use the port pipe_g3_rxpresethint[2:0] to turn on CTLE in triggered mode

during equalization phases.

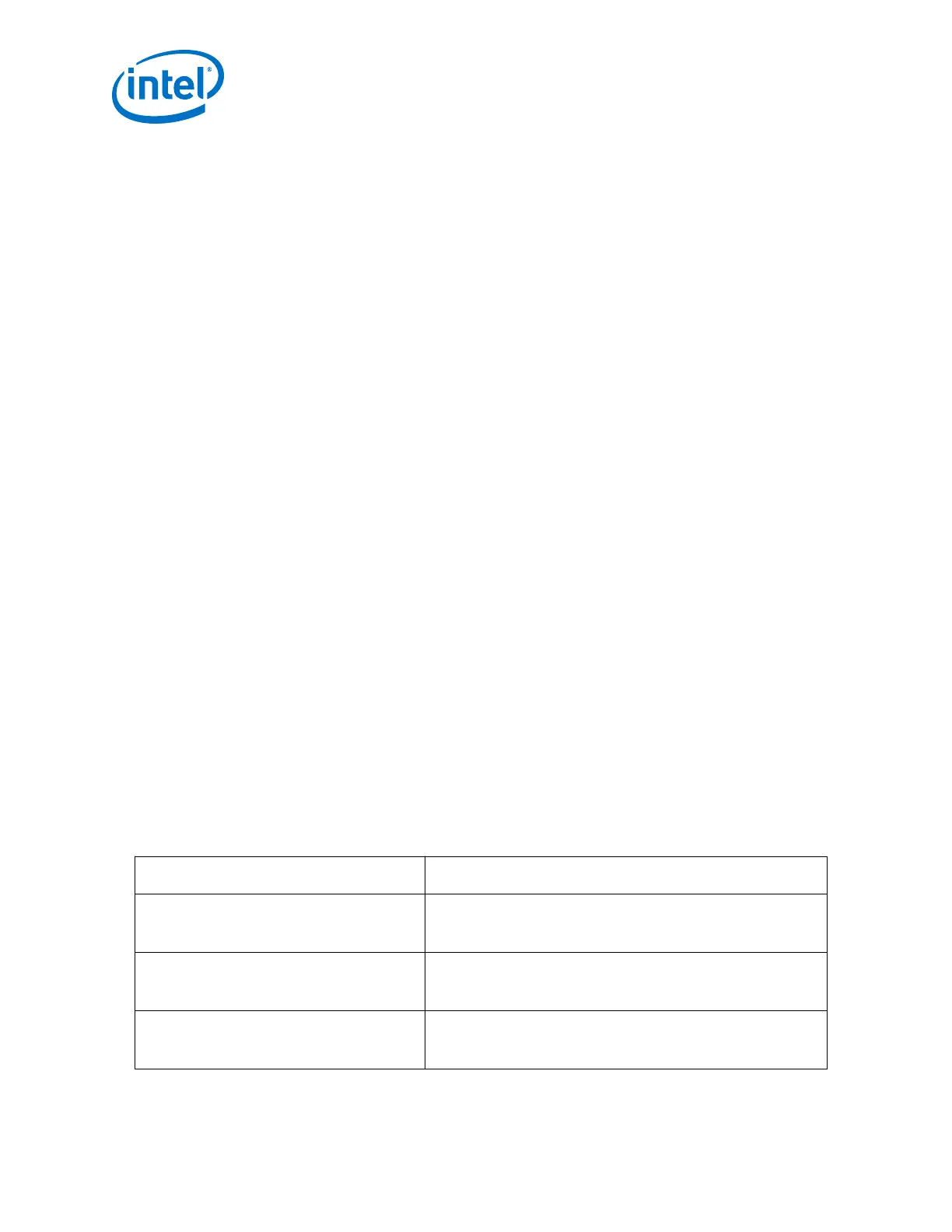

Table 196. CTLE mode for Gen1/Gen2 speeds of Gen3 capable design

Use this table to drive the pipe_g3_rxpresethint port and set the CTLE in manual mode when operating at

Gen1/Gen2 speeds of a Gen3 capable design.

Gen3 capable design running at Gen1/Gen2

speeds during

Supported CTLE - mode Manual. To use CTLE in manual mode

Power up •

During power up, set pipe_g3_rxpresethint[2:0] = 3’b000

• You can use the default CTLE 4S AC Gain set by Quartus (or)

• Set the manual CTLE 4S AC Gain using QSF assignments

Down train to Gen1/Gen2 (directed or not) and

subsequent re-entry to Gen3

•

On entry to Gen1/2, set pipe_g3_rxpresethint[2:0] = 3’b000

• You can use the default CTLE 4S AC Gain set by Quartus (or)

• Set the manual CTLE 4S AC Gain using QSF assignments

Down train to Gen1/Gen2 •

On entry to Gen1/2, set pipe_g3_rxpresethint[2:0] = 3’b000

• You can use the default CTLE 4S AC Gain set by Quartus (or)

• Set the manual CTLE 4S AC Gain using QSF assignments

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

276

Loading...

Loading...