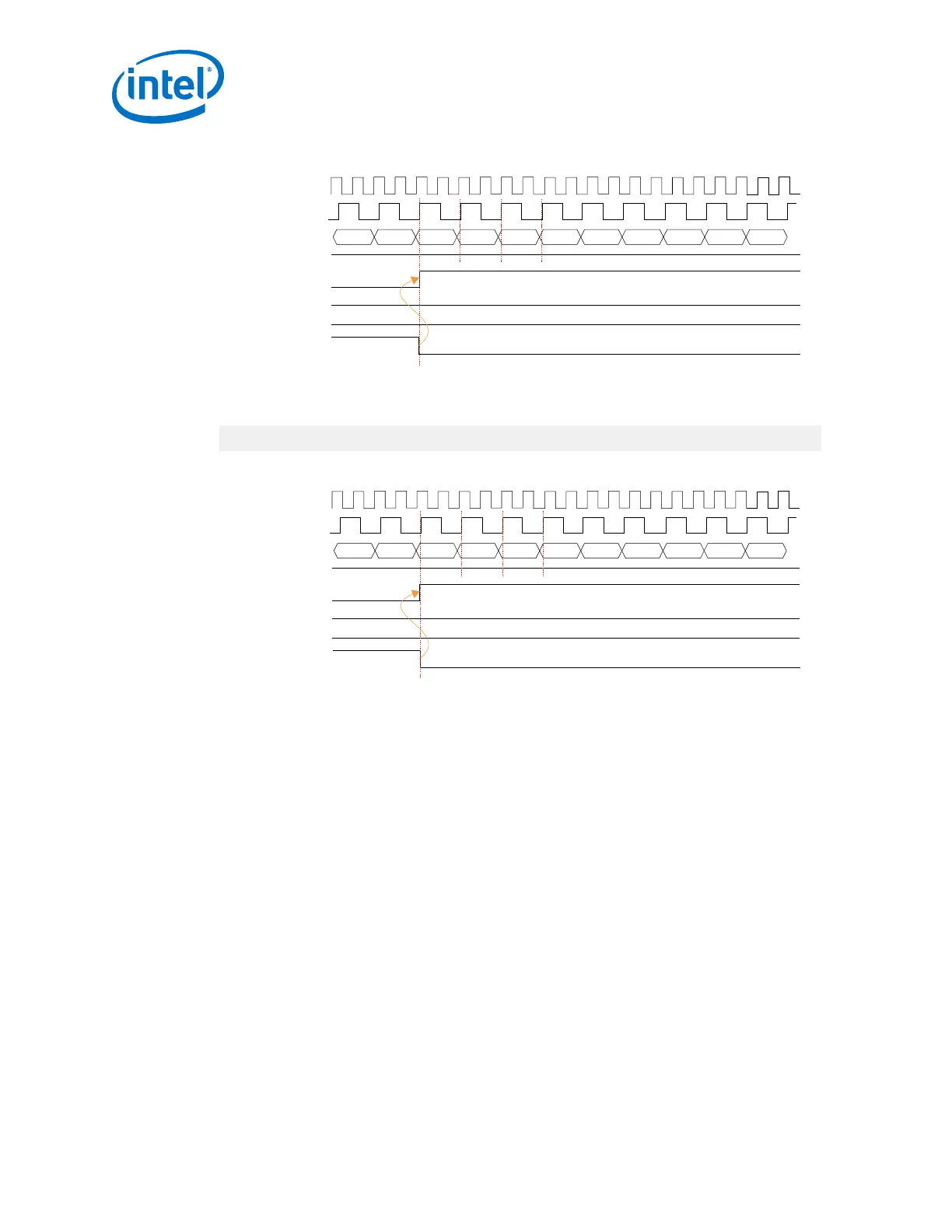

Figure 126. TX FIFO Basic Mode Operation

64’d0 64’d1 64’d2 64’d3 64’d4

64’d5 64’d6 64’d7 64’d8 64’d9 64’ha

tx_clkout (read side)

tx_coreclk (write side)

tx_parallel_data[63:0]

tx_digitalreset

tx_enh_datavalid

tx_fifo_pempty

tx_fifo_full

tx_fifo_pfull

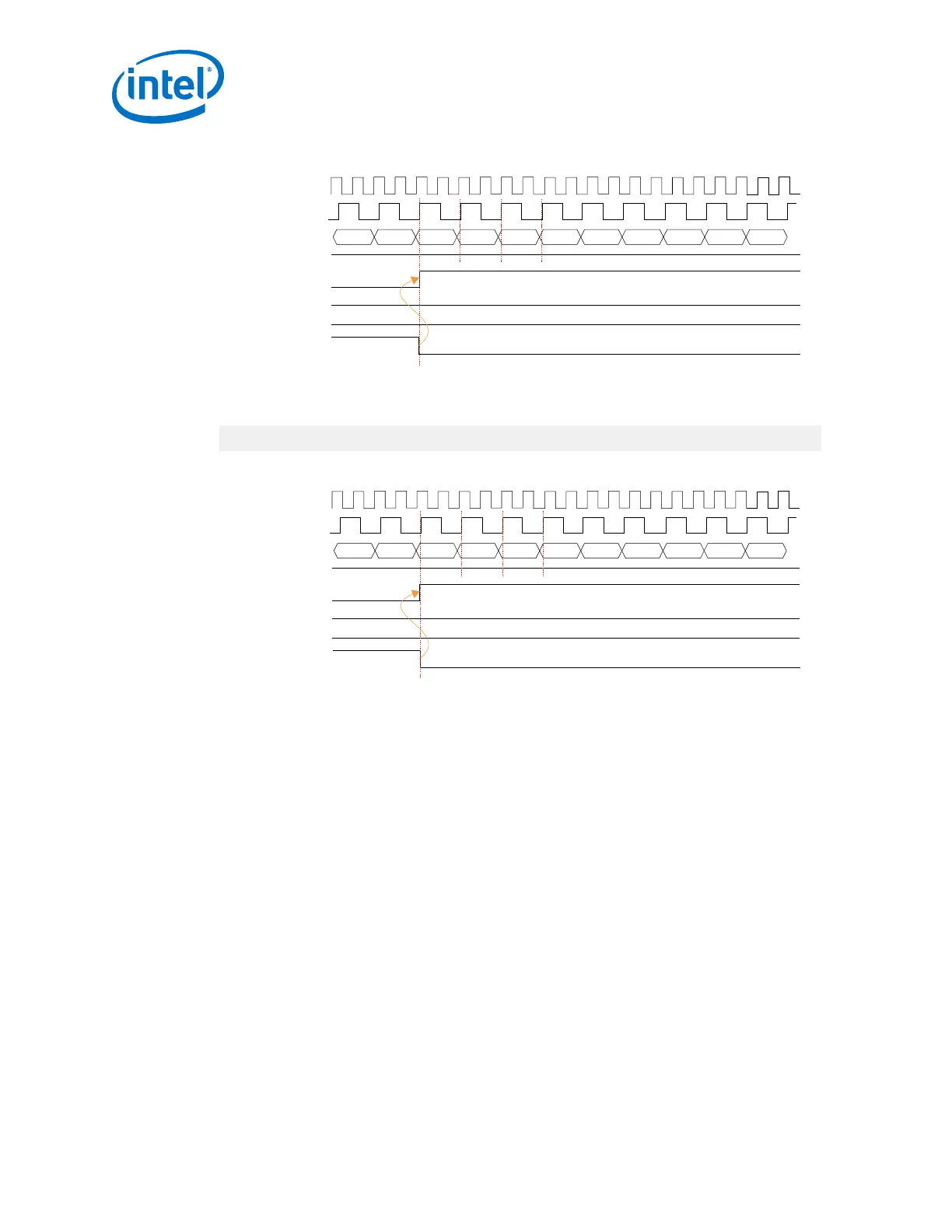

For RX FIFO, assert rx_enh_read_en with the rx_fifo_pempty signal going low.

This can be done with the following example assignment:

assign rx_enh_read_en = ~rx_fifo_pempty;

Figure 127. RX FIFO Basic Mode Operation

64’d0 64’d1 64’d2 64’d3 64’d4

64’d5 64’d6 64’d7 64’d8 64’d9 64’ha

rx_clkout (write side)

rx_coreclkin (read side)

rx_parallel_data[63:0]

rx_digitalreset

rx_enh_read_en

rx_fifo_pfull

rx_fifo_empty

rx_fifo_pempty

If you are using even gear ratios, the rx_enh_data_valid signal is always high. For

uneven gear ratios, rx_enh_data_valid toggles. RX parallel data is valid when

rx_enh_data_valid is high. Discard invalid RX parallel data when the

rx_enh_datavalid signal is low.

Register and Fast Register Mode

This FIFO mode is used for protocols, which require deterministic latency. You can tie

tx_fifo_wr_en to 1.

2.9.1.5. TX Data Bitslip

The bit slip feature in the TX gearbox allows you to slip the transmitter bits before

they are sent to the serializer.

The value specified on the TX bit slip bus indicates the number of bit slips. The

minimum slip is one UI. The maximum number of bits slipped is equal to the FPGA

fabric-to-transceiver interface width minus 1. For example, if the FPGA fabric-to-

transceiver interface width is 64 bits, the bit slip logic can slip a maximum of 63 bits.

Each channel has 6 bits to determine the number of bits to slip. The TX bit slip bus is

a level-sensitive port, so the TX serial data is bit slipped statically by TX bit slip port

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

298

Loading...

Loading...