64B/66B Encoder Reset Condition

The tx_digitalreset signal resets the 64B/66B encoder. During the reset

condition, the 64B/66B encoder does not output any signal in contrast with the

8B/10B encoder.

5.2.1.5. Pattern Generators

The Arria 10 transceivers contain hardened generators and checkers to provide a

simple and easy way to verify and characterize high speed links. Hardening the

pattern generators and checkers save FPGA core logic resources. The following pattern

generator blocks are supported in Arria 10:

• Pseudo Random Binary Sequence (PRBS)

• Pseudo Random Pattern (PRP)

Note: The pattern generators and checkers are supported for non-bonded channels only.

The pattern generators or checkers are enabled by writing to the respective register

bits of the Transceiver. Refer to the Reconfiguration Interface and Dynamic

Reconfiguration chapter for configuration details.

Related Information

Reconfiguration Interface and Dynamic Reconfiguration on page 502

5.2.1.5.1. PRBS Pattern Generator (Shared between Enhanced PCS and Standard PCS)

You can use Arria 10 pseudo-random bit sequence PRBS generator to simulate traffic

without developing or fully implementing any upper layer of a protocol stack. The

PRBS generator in Arria 10 devices is a shared hardened block between the Standard

and Enhanced datapaths through the PCS instead of being two unique instances: one

for Standard PCS and one for the Enhanced PCS. There is only one set of control

signals and registers for using this feature. The data lines from the various PCSes and

shared PRBS, are muxed before they are sent to the PMA. When the PRBS generator is

enabled, the data on the PRBS data lines is selected to be sent to the PMA. At any

instant, either the data from the PCS or the data generated from the PRBS generator,

is sent to the PMA.

The PRBS generator can be configured for two widths of the PCS-PMA interface: 10

bits and 64 bits. PRBS9 is available in 10-bit and 64-bit PCS-PMA widths. All other

PRBS patterns are available in 64-bit PCS-PMA width only. The PRBS generator

patterns can only be used when PCS-PMA interface width is configured to 10 bits or 64

bits.

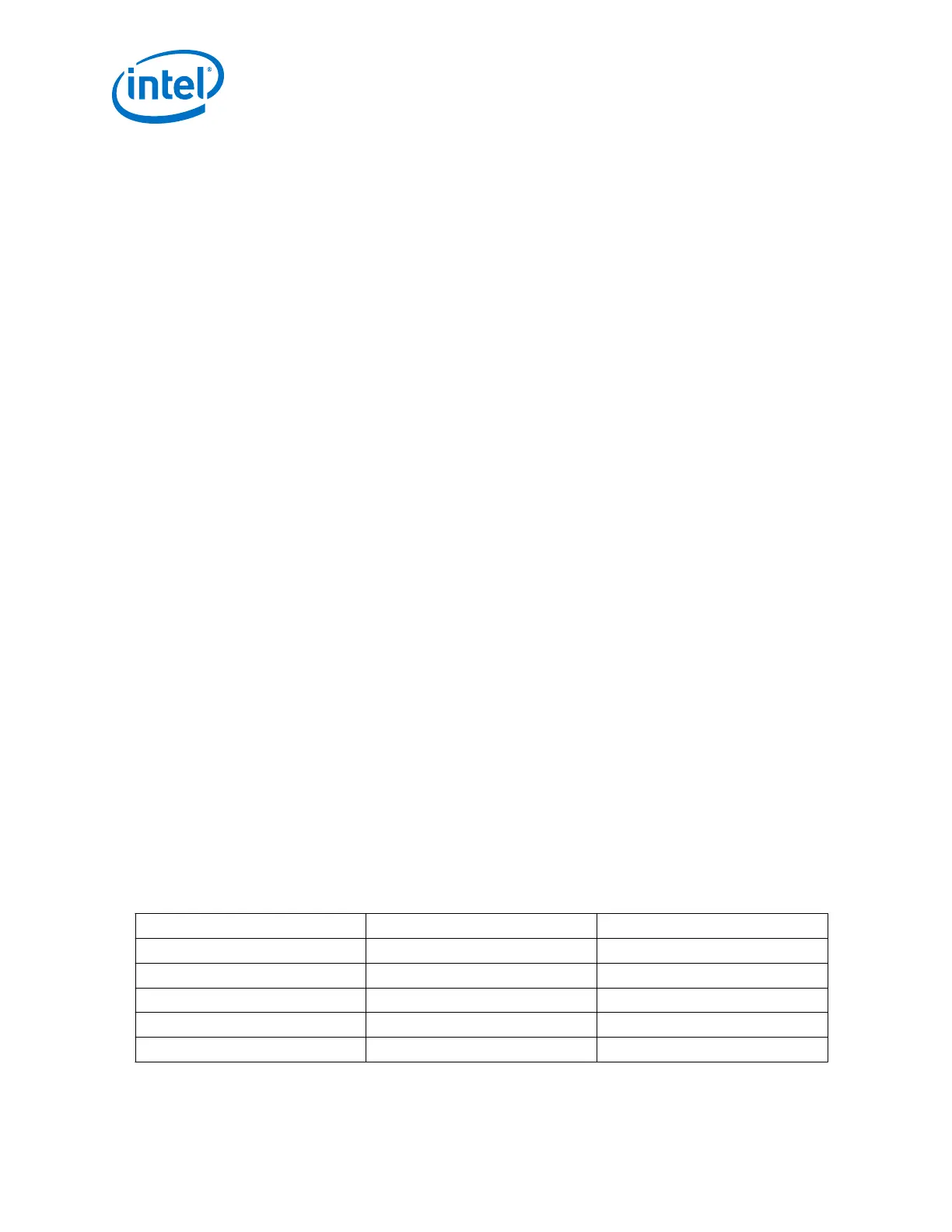

Table 254. Supported PRBS Patterns

PRBS Pattern 10 bit PCS-PMA width 64 bit PCS-PMA width

PRBS7: x

7

+ x

6

+ 1 Yes

PRBS9: x

9

+ x

5

+ 1 Yes Yes

PRBS15: x

15

+ x

14

+ 1 Yes

PRBS23: x

23

+ x

18

+ 1 Yes

PRBS31: x

31

+ x

28

+ 1 Yes

5. Arria 10 Transceiver PHY Architecture

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

466

Loading...

Loading...