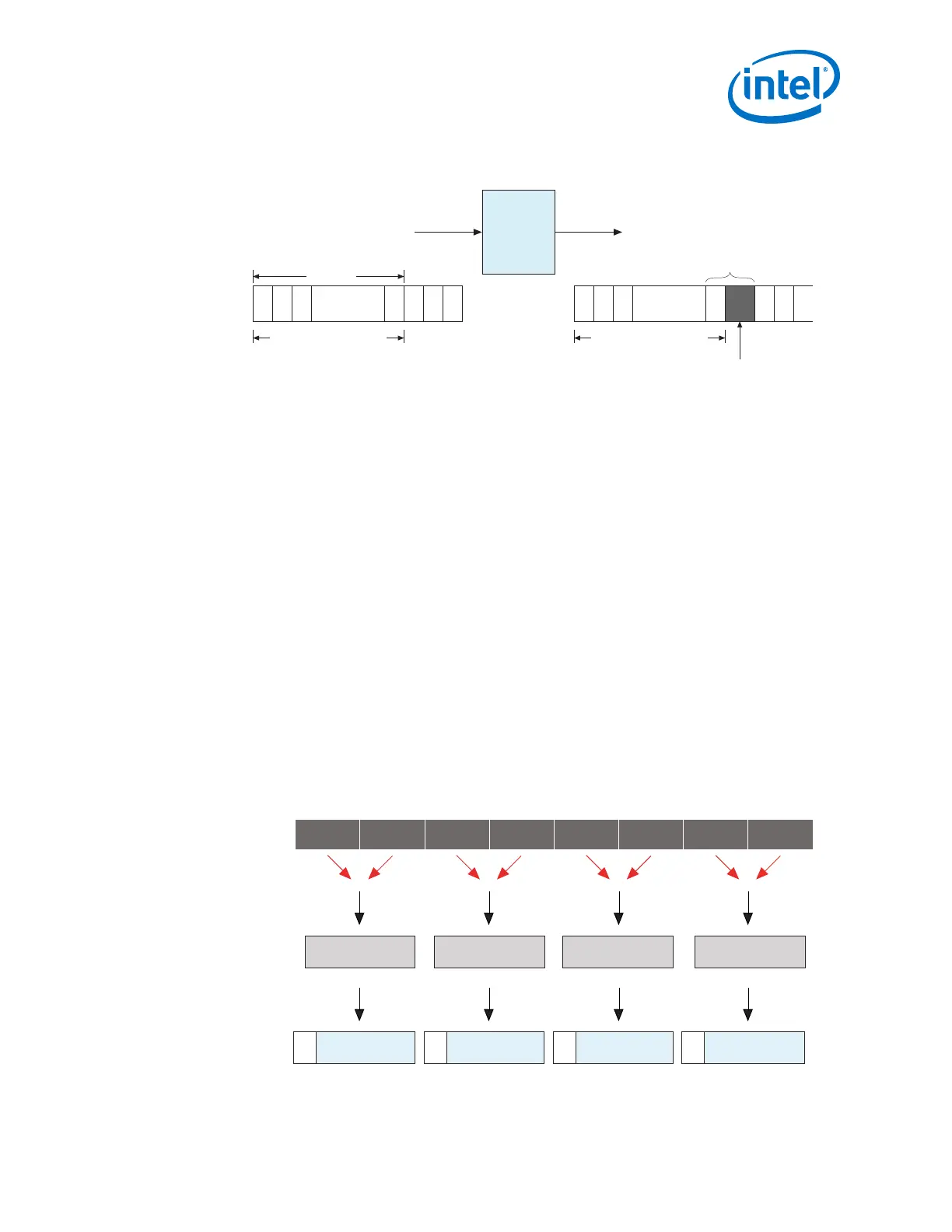

Figure 238. Interlaken CRC-32 Generator

The Interlaken CRC-32 generator implements the Interlaken protocol.

Interlaken

CRC-32

Generator

Payload

Total Data for CRC-32 Calculation

Metaframe

From the Interlaken Frame Generator

Metaframes with Embedded

CRC-32 Code to Scrambler

Di

Di

Sy

0 0 066676767

SB SKSy SB SK Payload

Total Data for CRC-32 Calculation

Calculated CRC-32 Value

Inserted in the 32 Bits

of Diagnostic Word

Sy

31 066

SB SKSy SB SK

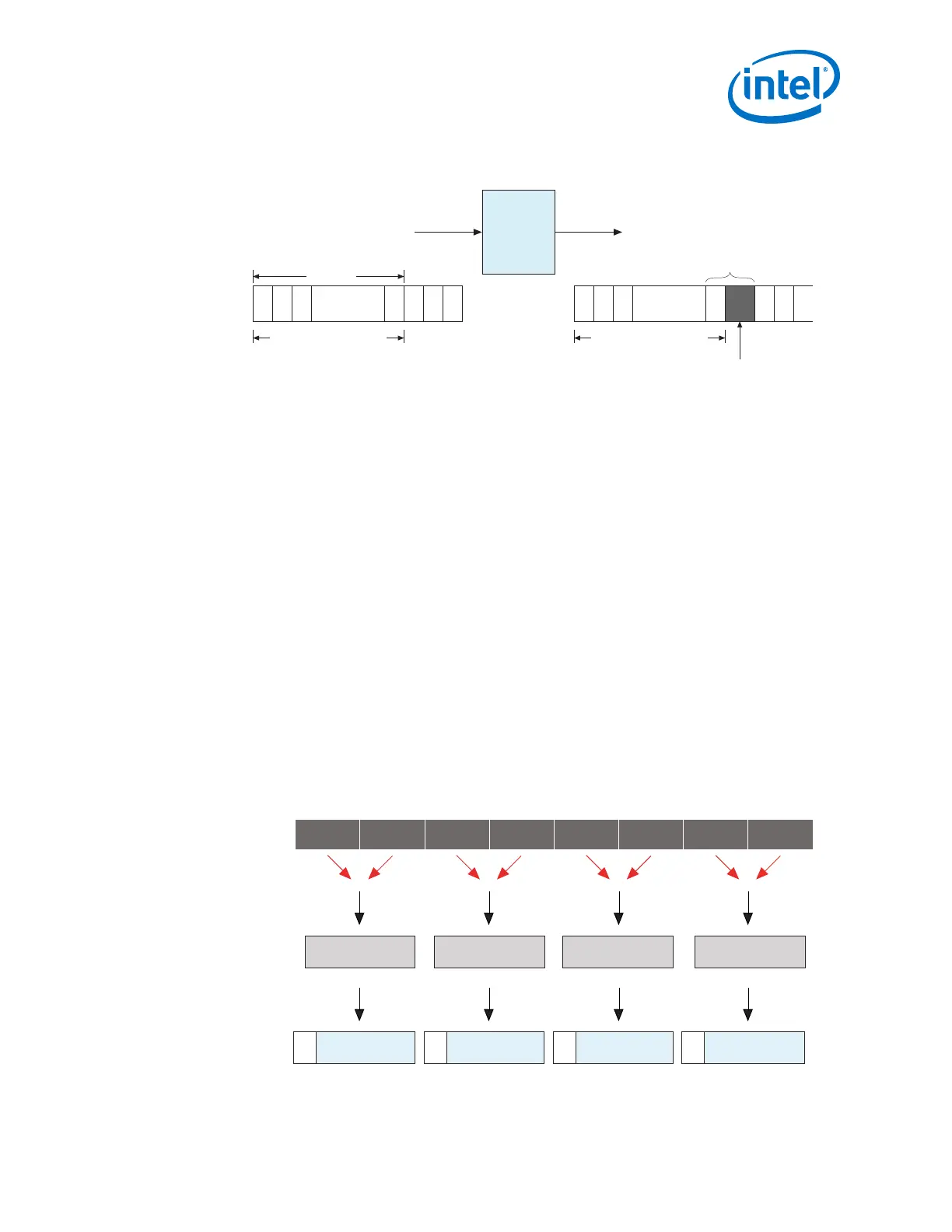

5.2.1.4. 64B/66B Encoder and Transmitter State Machine (TX SM)

The 64B/66B encoder is used to achieve DC-balance and sufficient data transitions for

clock recovery. It encodes 64-bit XGMII data and 8-bit XGMII control into 10GBASE-R

66-bit control or data blocks in accordance with Clause 49 of the IEEE802.3-2008

specification.

The 66-bit encoded data contains two overhead sync header bits that the receiver PCS

uses for block synchronization and bit-error rate (BER) monitoring. The sync header is

01 for data blocks and 10 for control blocks. Sync headers are not scrambled and are

used for block synchronization. (The sync headers 00 and 11 are not used, and

generate an error if seen.) The remainder of the block contains the payload. The

payload is scrambled and the sync header bypasses the scrambler.

The encoder block also has a state machine (TX SM) designed in accordance with the

IEEE802.3-2008 specification. The TX SM ensures valid packet construction on data

sent from the MAC layer. It also performs functions such as transmitting local faults

under reset, as well as transmitting error codes when the 10GBASE-R PCS rules are

violated.

Note: The 64B/66B encoder is available to implement the 10GBASE-R protocol.

Figure 239. Example Data Pattern for 64B/66B Encoding

C

0

C

1

C

2

C

3

C

4

C

5

C

6

C

7

10

PCS

TXC<0:3> TXD<0:31> XGMII

Data

XGMII

data

66-bit

encoded

data

1e 000000 00000000

0 65

0 63

10 b4 D

0

D

1

D

2

0000000010 78 D

1

D

2

D

3

D

4

D

5

D

6

D

7

01 D

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

S

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

D

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

D

0

D

1

D

2

T

3

C

0

C

1

C

2

C

3

f07070707 f07070707f07070707 8 fb D

1

D

2

D

3

0 D

4

D

5

D

6

D

7

0 D

0

D

1

D

2

D

3

1 D

0

D

1

D

2

fd0 D

4

D

5

D

6

D

7

5. Arria 10 Transceiver PHY Architecture

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

465

Loading...

Loading...