5.2.1.6. Scrambler

The scrambler randomizes data to create transitions to DC-balance the signal and help

CDR circuits. The scrambler uses a x

58

+ x

39

+1 polynomial and supports both

synchronous scrambling used for Interlaken and asynchronous (also called self-

synchronized) scrambling used for the 10GBASE-R protocol.

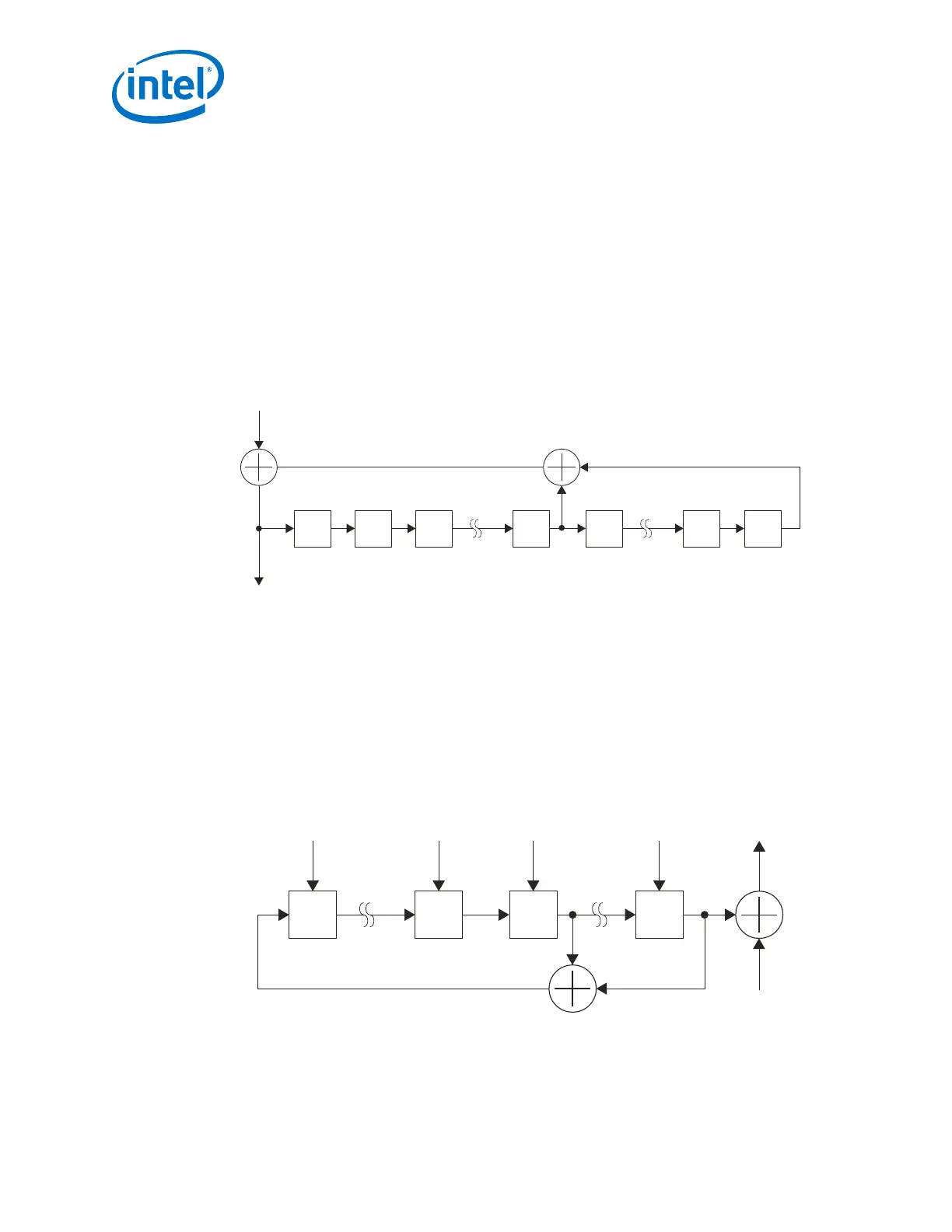

The asynchronous (self-synchronizing) mode does not require an initialization seed.

Except for the two sync header bits in each 66-bit data block, the entire 64-bit

payload is scrambled by feeding it into a linear feedback shift register (LFSR)

continuously to generate scrambled data while the sync-header bits bypass the

scrambler. The initial seed is set to all 1s. You can change the seed for the 10GBASE-R

protocol using the Native PHY IP Parameter Editor.

Figure 241. Asynchronous Scrambler in Serial Implementation

S0 S1 S38 S39 S56

OUT

IN

S2 S57

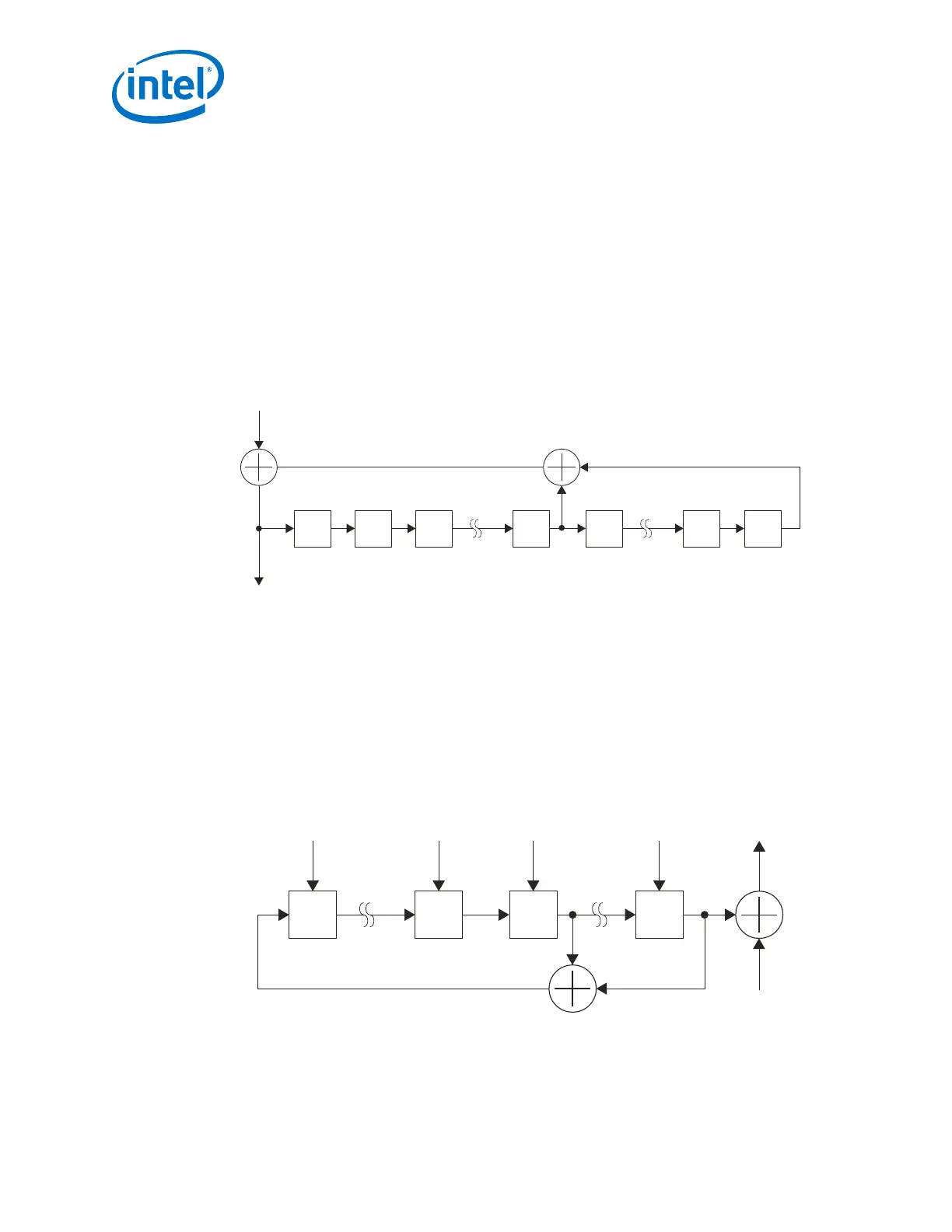

In synchronous mode, the scrambler is initially reset to different programmable seeds

on each lane. The scrambler then runs by itself. Its current state is XOR’d with the

data to generate scrambled data. A data checker in the scrambler monitors the data to

determine if it should be scrambled or not. If a synchronization word is found, it is

transmitted without scrambling. If a Scrambler State Word is detected, the current

scramble state is written into the 58-bit scramble state field in the Scrambler State

Word and sent over the link. The receiver uses this scramble state to synchronize the

descrambler. The seed is automatically set for Interlaken protocol.

Figure 242. Synchronous Scrambler Showing Different Programmable Seeds

37 38 570

IN

OUT

LFSR Seed

S0 S37 S38 S57

5. Arria 10 Transceiver PHY Architecture

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

468

Loading...

Loading...