The PMA analog settings can be broadly divided into the following groups:

• PMA analog settings that are channel or system dependent:

— These settings may vary from channel to channel based on channel loss or

other factors

— You can set these PMA analog settings based on IBIS-AMI or Advanced Link

Analyzer simulations

— You can set these PMA analog settings using QSF assignments or by

performing RMWs to the respective registers

— These PMA analog settings are not included in the configuration files by

default. To include these PMA analog settings in the configuration files, you

must enable the Include PMA Analog settings in configuration files

option in the Dynamic Reconfirmation tab of the Transceiver Native PHY IP

Parameter Editor. Enabling this feature adds the PMA analog settings specified

in the Analog PMA settings (Optional) tab of the Native PHY IP Parameter

Editor to the configuration files. Even with this option enabled in the Native

PHY IP Parameter Editor, you must still specify QSF assignments for your

analog settings when compiling your static design. The analog settings

selected in the Native PHY IP Parameter Editor are used only to include these

settings and their dependent settings in the selected configuration files. For

details about optional analog settings, refer to the "Analog PMA Settings

(Optional) for Dynamic Reconfiguration" table in the Ports and Parameters

section. For details about QSF assignments for the analog settings, refer to the

Analog Parameter Settings chapter.

— If you do not enable the Include PMA Analog settings in configuration

files option, then you can change these analog settings by performing RMWs

using direct reconfiguration flow

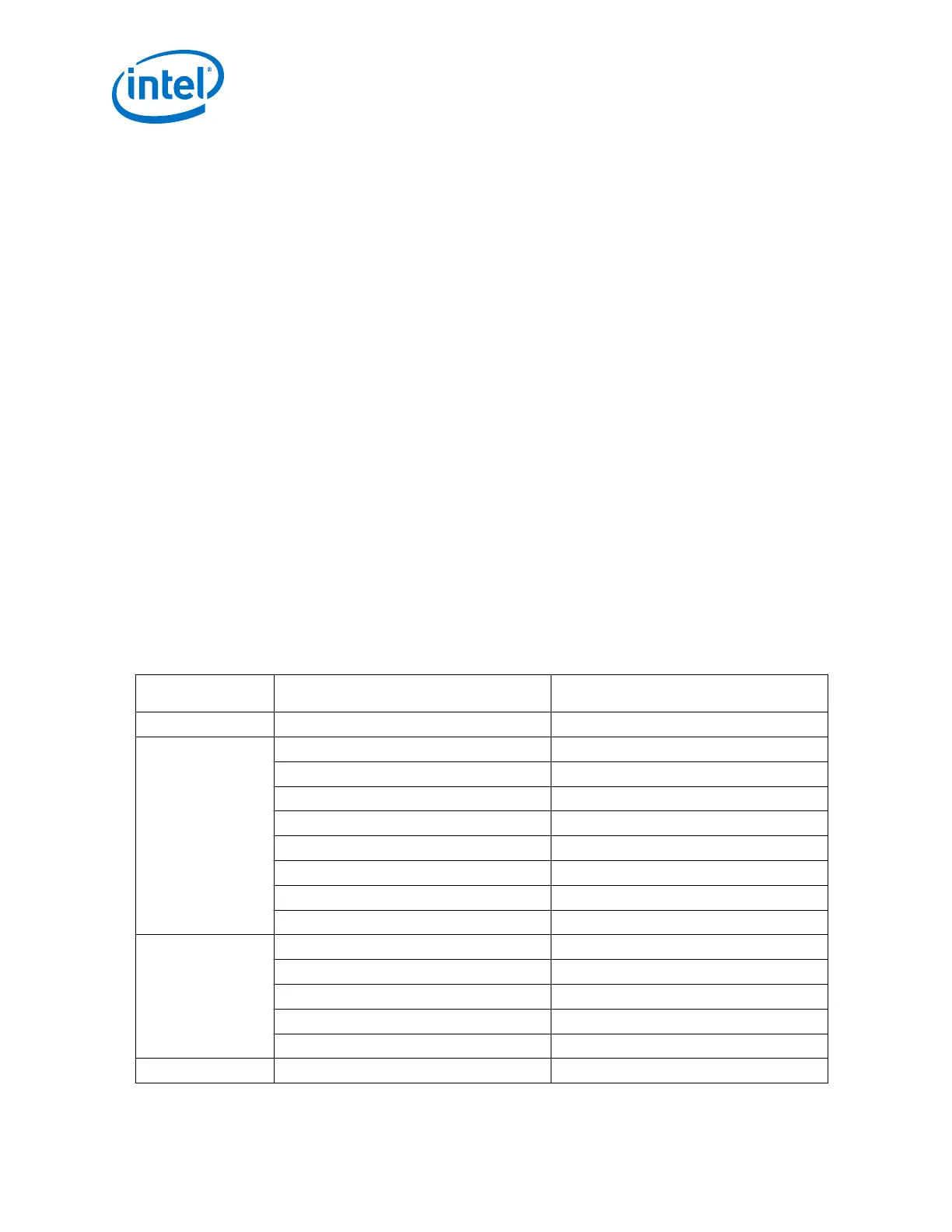

Table 272. PMA Analog Settings that are Channel or System Dependent

PMA Analog Feature Fitter Report Name Arria 10 Transceiver Register Map Attribute

Name

VOD vod_output_swing_ctrl vod_output_swing_ctrl

Pre-emphasis pre_emp_sign_1st_post_tap pre_emp_sign_1st_post_tap

pre_emp_sign_2nd_post_tap pre_emp_sign_2nd_post_tap

pre_emp_sign_pre_tap_1t pre_emp_sign_pre_tap_1t

pre_emp_sign_pre_tap_2t pre_emp_sign_pre_tap_2t

pre_emp_switching_ctrl_1st_post_tap pre_emp_switching_ctrl_1st_post_tap

pre_emp_switching_ctrl_2nd_post_tap pre_emp_switching_ctrl_2nd_post_tap

pre_emp_switching_ctrl_pre_tap_1t pre_emp_switching_ctrl_pre_tap_1t

pre_emp_switching_ctrl_pre_tap_2t pre_emp_switching_ctrl_pre_tap_2t

CTLE eq_dc_gain_trim eq_dc_gain_trim

one_stage_enable one_stage_enable

eq_bw_sel eq_bw_sel

adp_ctle_eqz_1s_sel adp_ctle_eqz_1s_sel

adp_ctle_acgain_4s adp_ctle_acgain_4s

VGA adp_vga_sel adp_vga_sel

6. Reconfiguration Interface and Dynamic Reconfiguration

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

528

Loading...

Loading...