RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1190

Dec 10, 2015

(23) UART Option Register 1 (LUORn1)

Address: F06E1H

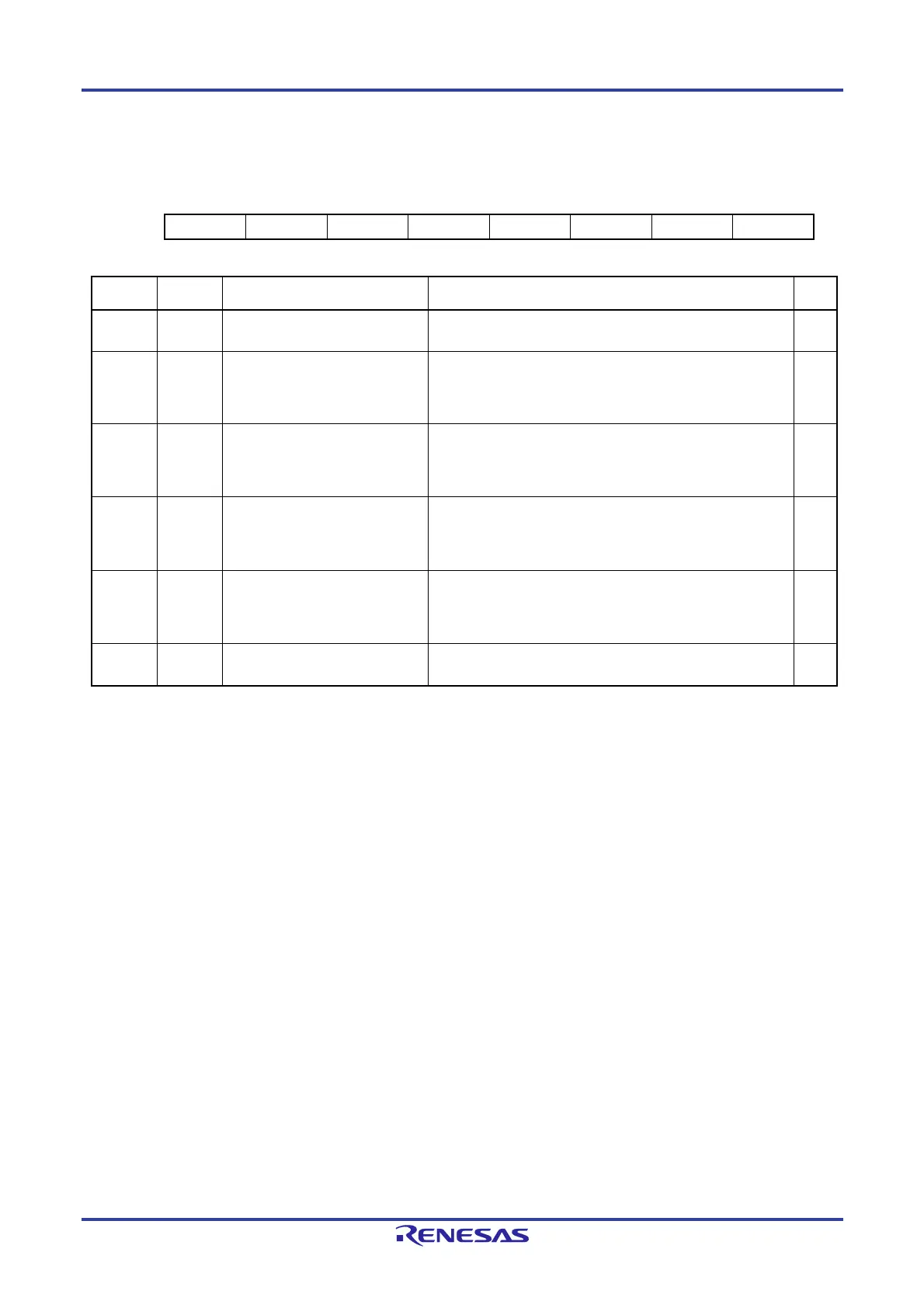

7 6 5 4 3 2 1 0

— — — UECD UTIGTS UEBDCE UEBDL UEBE

Value after reset:

0 0 0 0 0 0 0 0

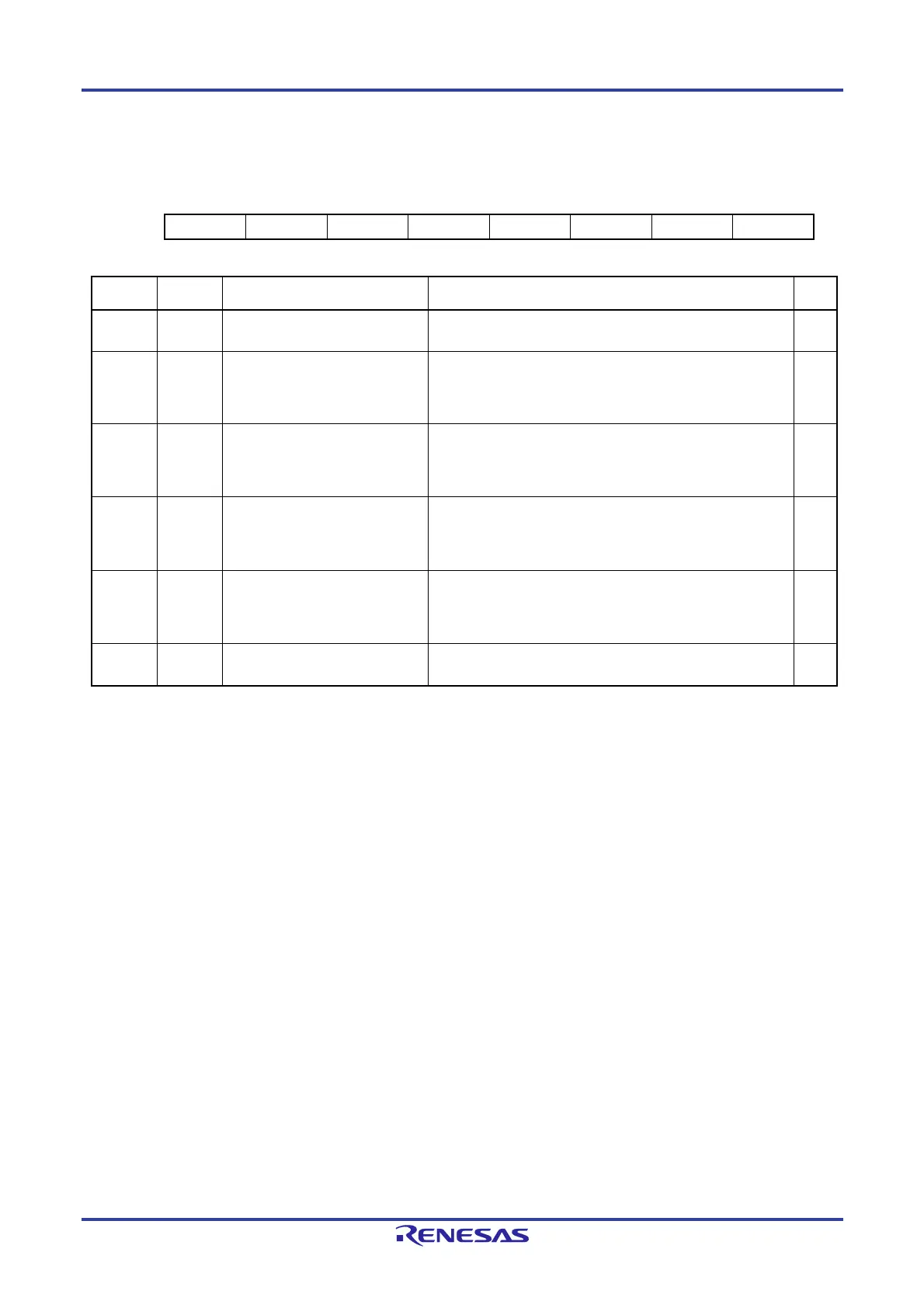

Bit Symbol Bit Name Function R/W

0 UEBE Expansion Bit Enable 0: Disables expansion bit operation.

1: Enables expansion bit operation.

R/W

1 UEBDL Expansion Bit Detection Level

Select

0: Selects expansion bit value 0 as the expansion bit detection

level.

1: Selects expansion bit value 1 as the expansion bit detection

level.

R/W

2 UEBDCE Expansion Bit/Data Comparison

Enable

0: Disables data comparison after detection of the expansion

bit.

1: Enables data comparison after detection of the expansion

bit.

R/W

3 UTIGTS Transmission Interrupt Generation

Timing Select

0: Transmission interrupt is generated at the start of

transmission.

1: Transmission interrupt is generated at the completion of

transmission.

R/W

4 UECD Expansion Bit Comparison Disable 0: Enables comparison between the received expansion bit and

the UEBDL bit value.

1: Disables comparison between the received expansion bit

and the UEBDL bit value.

R/W

7 to 5 — Reserved These bits are always read as 0. The write value should always

be 0.

R/W

UEBE bit (expansion bit enable bit)

The UEBE bit enables or disables expansion bit operation.

With 0 set, expansion bit operation is disabled.

With 1 set, expansion bit operation is enabled.

Set this bit when the OMM0 bit in the LMSTn register is 0 (LIN reset mode).

Do not set this bit to 1 when the UART buffer is in use.

UEBDL bit (expansion bit detection level select bit)

The UEBDL bit sets the level to be detected as the expansion bit when the UEBE bit is 1 (expansion bit operation is enabled)

and the UECD bit is 0 (comparison of the expansion bit is enabled).

With 0 set, expansion bit value 0 is the level to be detected as the expansion bit.

With 1 set, expansion bit value 1 is the level to be detected as the expansion bit.

Set this bit when the OMM0 bit in the LMSTn register is 0 (LIN reset mode).

Do not set this bit to 1 when the UART buffer is in use.

Loading...

Loading...