RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1223

Dec 10, 2015

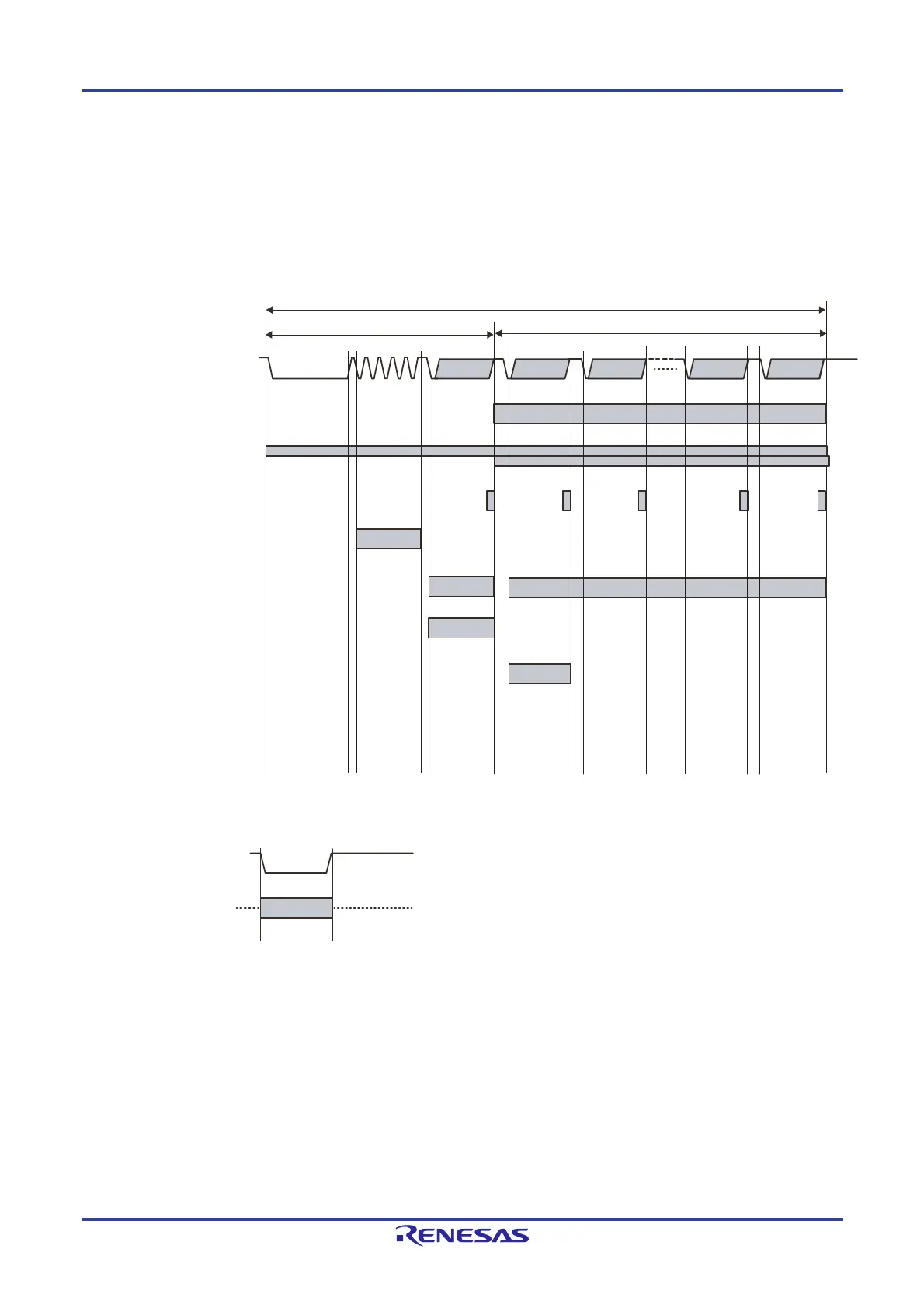

(b) Target Time Area for LIN Error Detection

Figure 17-21 shows the time domain in which the LIN/UART module in slave mode performs monitoring for error

detection.

Figure 17-21. Target Time Area for LIN Error Detection (LIN Slave Mode)

<Frame transmission/reception>

Header

Frame

Response

Break field

Sync field ID field Data 1

Data 2 Data 8 Checksum

In transmission only

Only stop bit in reception

In reception only

Only in reception

with enhance

checksum mode

selected

<Wake-up transmission>

Bit error

Frame timeout error

Response timeout error

Framing error

Sync field error

ID parity error

Response preparation error

Checksum error

Wake-up

Bit error

Loading...

Loading...