RL78/F13, F14 CHAPTER 19 DTC

R01UH0368EJ0210 Rev.2.10 1458

Dec 10, 2015

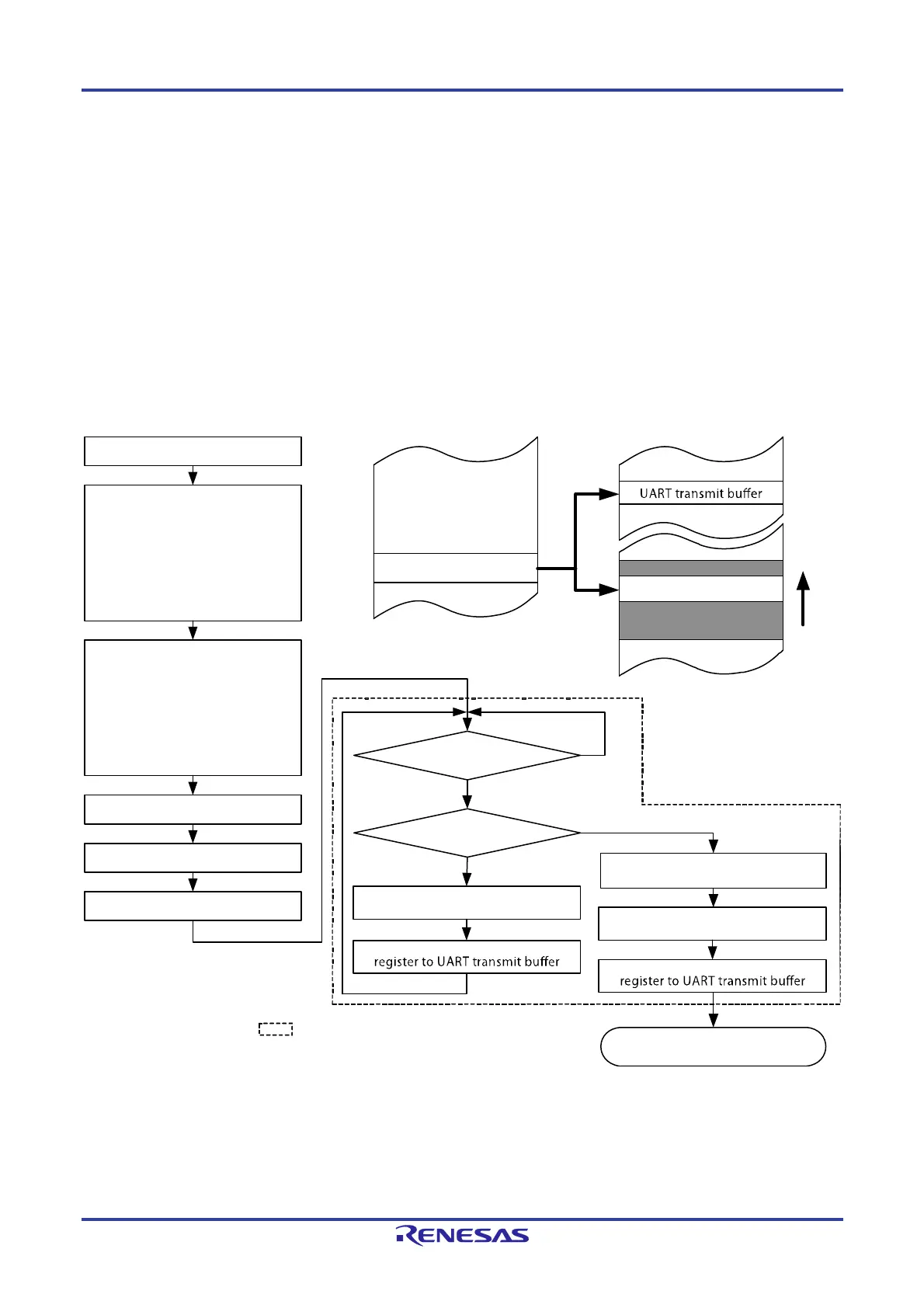

(1) Example of using chain transfers: Consecutively capturing A/D conversion results and UART transmission

The DTC is activated by an A/D conversion end interrupt and A/D conversion results are transferred to RAM, and

then transmitted using the UART.

The vector address is FFB09H.

Control data of capturing A/D conversion results is allocated at FFBA0H to FFBA7H.

Control data of UART transmission is allocated at FFBA8H at FFBAFH.

An A/D conversion end interrupt is assigned to source number 9.

Transfers 2-byte data of the A/D conversion result register (FFF1FH, FFF1EH) to FFD80H to FFDCFH of RAM,

and transfers the upper 1 byte (FFF1FH) of the A/D conversion result register to the UART transmit buffer

(FFF10H).

Figure 19-27. Example of Using Chain Transfers: Consecutively Capturing A/D Conversion Results and UART

Transmission

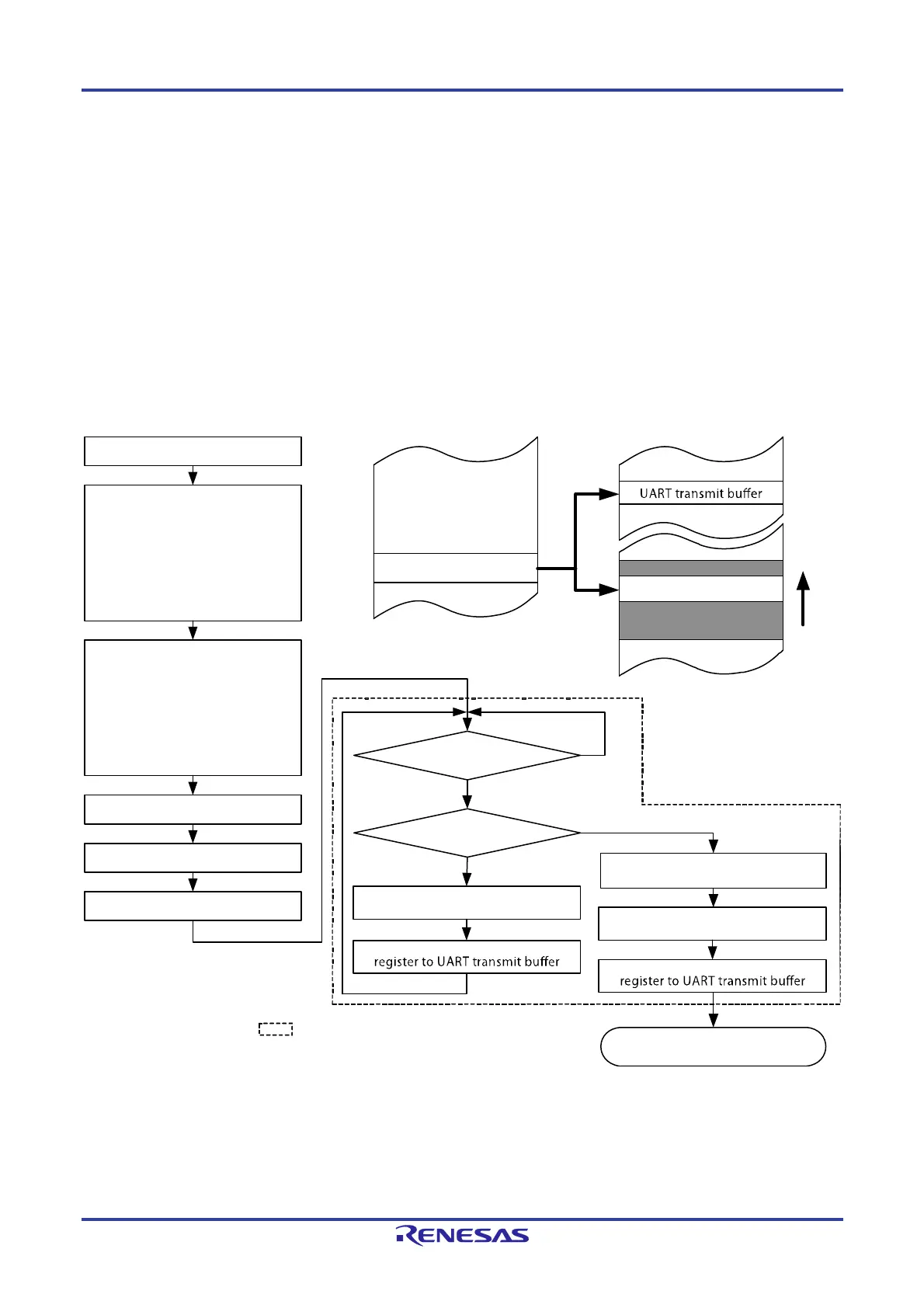

Cautions 1. Set the CHNE bit in the DTCCR23 register to 0 (chain transfers disabled).

2. For chain transfer, in the second and subsequent data transfers, bits DTCENi0 to DTCENi7 (i = 0 to

5

Note

) in the DTCENi register are not set to 0 (DTC activation disabled), and no interrupt request is

generated.

Note Products of groups A, B, C, and D: i = 0 to 4

Products of group E: i = 0 to 5

RAM

A/D conversion result

register

DTCBAR= FBH

DTCEN16 = 1

UART setting

Starting A/D conversion

No

Transfer from A/D conversion

result register to RAM

Yes

Yes

No

A/D conversion

end interrupt?

Transfer from A/D conversion result

Interrupt handling

FDCEH

FD80H

Transfer from A/D conversion

result register to RAM

Transfer from A/D conversion result

The processing show n inside the dotted

line is automatically executed by the DTC.

Setting control data of capturing

A/D conversion results

Vector address (FFB09H) =A0H

DTCCR12 (FFBA0H) = 58H

DTBLS12 (FFBA1H) = 01H

DTCCT12 (FFBA2H) = 50H

DTRLD12 (FFBA3H) = 50H

DTSAR12 (FFBA4H) = FF1EH

DTDAR12 (FFBA6H) = FD80H

Setting control data

of UART transmission

Vector address (FFB11H) = A8H

DTCCR13(FFBA8H) = 00H

DTBLS13(FFBA9H) = 01H

DTCCT13(FFBAAH) = 00H

DTRLD13(FFBABH) = 00H

DTSAR13(FFBACH) = FF1FH

DTDAR13(FFBAEH) = FF10H

Occurrence of interrupt

corresponding to source number 9

DTCEN16 = 0

DTCCT12 = 01H?

Loading...

Loading...