RL78/F13, F14 CHAPTER 3 CPU ARCHITECTURE

R01UH0368EJ0210 Rev.2.10 124

Dec 10, 2015

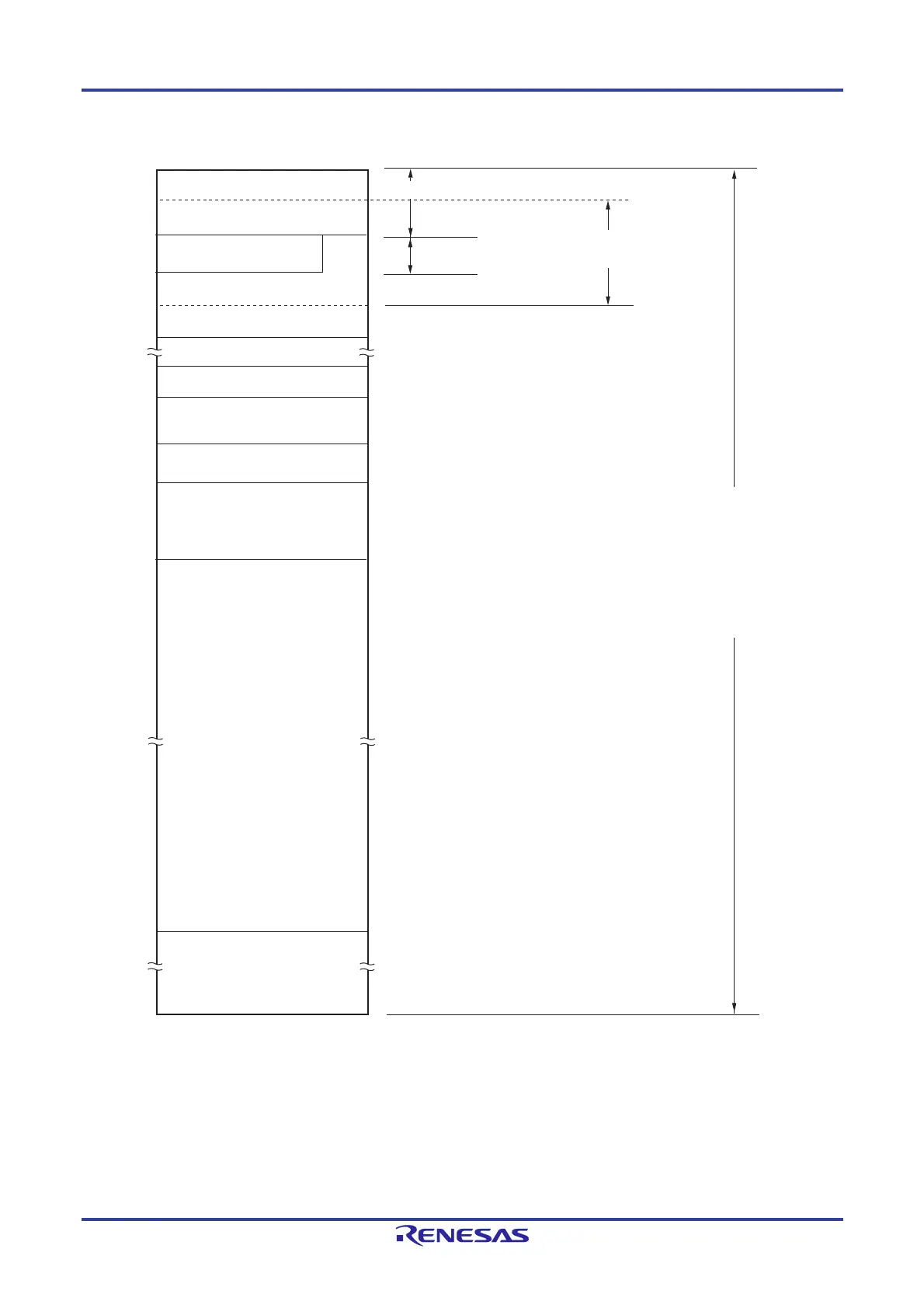

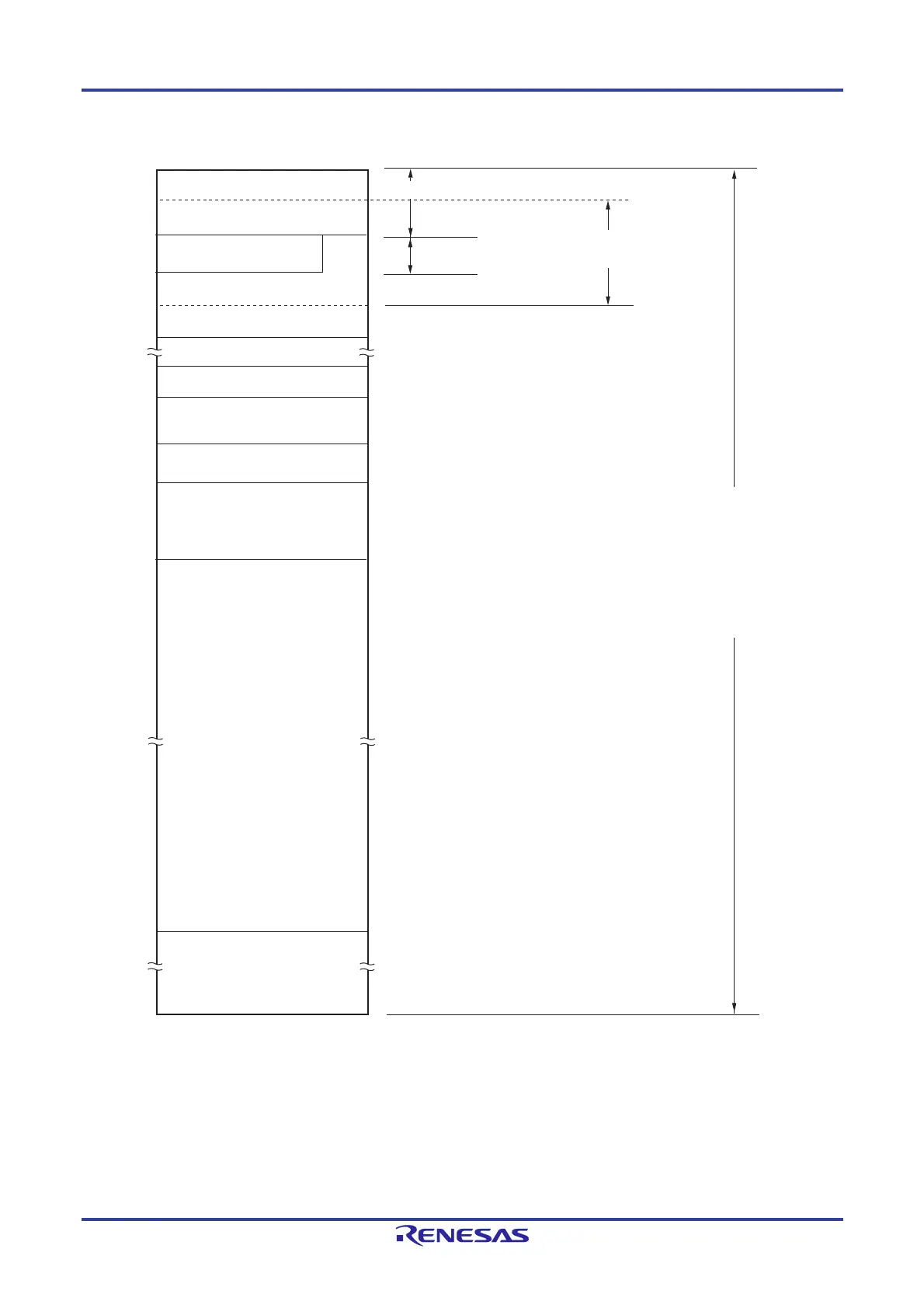

Figure 3-20. Correspondence between Data Memory and Addressing (R5F10AmC (m = 6, A, B, G, L))

Caution When executing instructions from the RAM area, be sure to initialize the used RAM area + 10 bytes

with any desired value.

Special function register (SFR)

256 bytes

General-purpose register

32 bytes

Code flash memory

32 KB

Special function register (2nd SFR)

2 KB

Mirror

24 KB

Reserved

Reserved

Reserved

RAM

2 KB

Data flash memory

4 KB

Register addressing

FFFFFH

00000H

FFF00H

FFEFFH

FFEE0H

FFEDFH

F0800H

F07FFH

F0000H

EFFFFH

08000H

07FFFH

FF700H

FF6FFH

F2000H

F1FFFH

F1000H

F0FFFH

FFE20H

FFE1FH

FFF20H

FFF1FH

F8000H

F7FFFH

Direct addressing

Register indirect addressing

Based addressing

Based indexed addressing

SFR addressing

Short direct

addressing

Loading...

Loading...