RL78/F13, F14 CHAPTER 27 SAFETY FUNCTIONS

R01UH0368EJ0210 Rev.2.10 1598

Dec 10, 2015

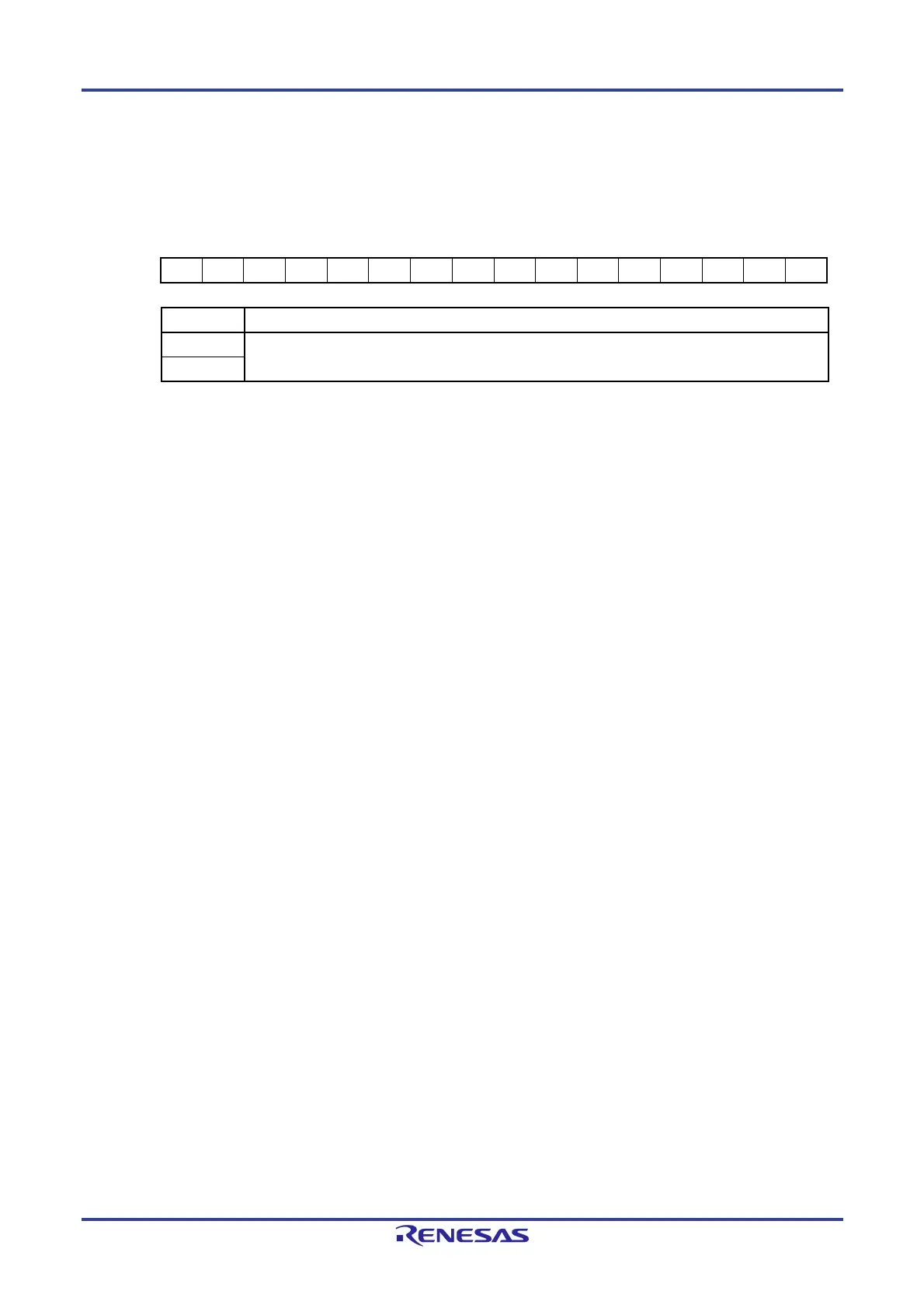

(3) SP underflow address setting register (SPUFR)

Figure 27-17. Format of SP Underflow Address Setting Register (SPUFR)

Address: F00DCH After reset: 0000H R/W

Symbol 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SPUFR - - - - - - - - - - - - - - - -

- Stack pointer underflow address setting

0 Stack pointer underflow address

1

Cautions 1. The lowest bit is fixed to 0.

2. If the values of bits 15 to 1 in stack pointer are smaller than the specified values of bits

15 to 1 in SPUFR, an interrupt signal (INTSPM) is generated.

Stack pointer < SPUFR: INTSPM interrupt signal is generated.

3. When SPMEN = 1, writing to SPUFR is invalid.

Loading...

Loading...