RL78/F13, F14 CHAPTER 3 CPU ARCHITECTURE

R01UH0368EJ0210 Rev.2.10 156

Dec 10, 2015

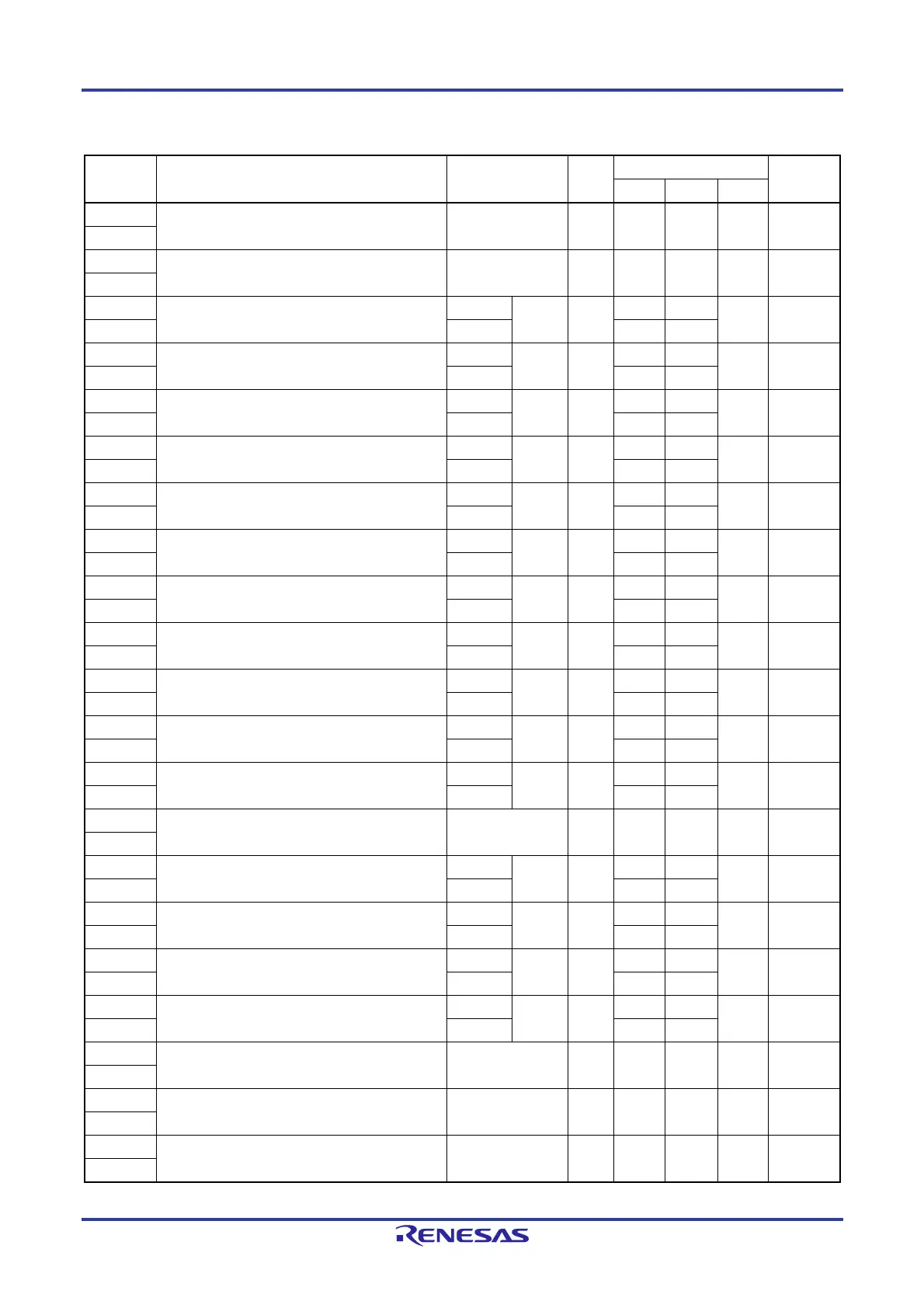

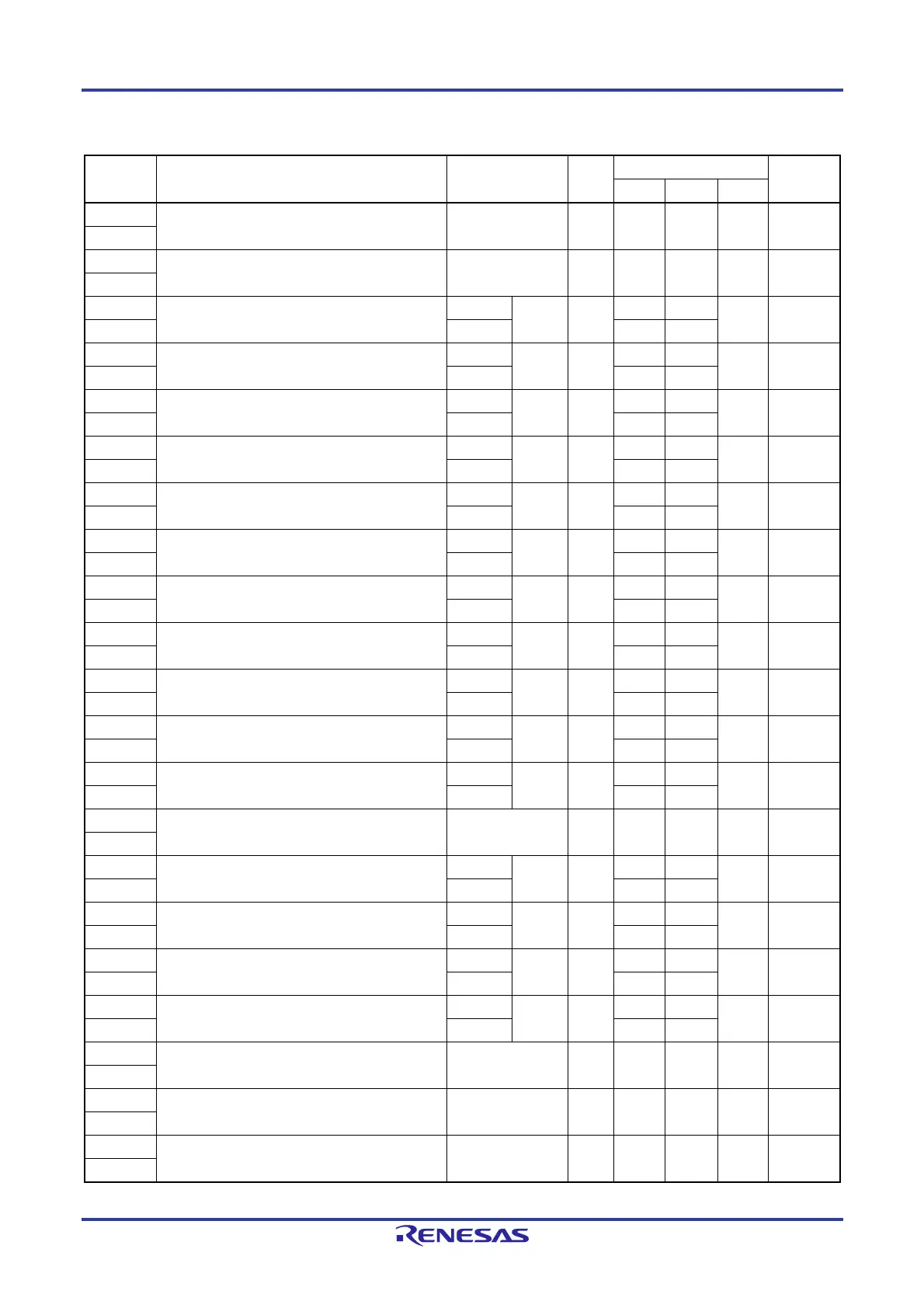

Table 3-6. Extended SFR (2nd SFR) List (5/32)

Address Special Function Register (2nd SFR) Name Symbol R/W Manipulable Bit Range After reset

1-bit 8-bit 16-bit

F019CH Timer mode register 06 TMR06 R/W – – 0000H

F019DH

F019EH Timer mode register 07 TMR07 R/W – – 0000H

F019FH

F01A0H Timer status register 00 TSR00L TSR00 R – 0000H

F01A1H – – –

F01A2H Timer status register 01 TSR01L TSR01 R – 0000H

F01A3H – – –

F01A4H Timer status register 02 TSR02L TSR02 R – 0000H

F01A5H – – –

F01A6H Timer status register 03 TSR03L TSR03 R – 0000H

F01A7H – – –

F01A8H Timer status register 04 TSR04L TSR04 R – 0000H

F01A9H – – –

F01AAH Timer status register 05 TSR05L TSR05 R – 0000H

F01ABH – – –

F01ACH Timer status register 06 TSR06L TSR06 R – 0000H

F01ADH – – –

F01AEH Timer status register 07 TSR07L TSR07 R – 0000H

F01AFH – – –

F01B0H Timer channel enable status register 0 TE0L TE0 R 0000H

F01B1H – – –

F01B2H Timer channel start register 0 TS0L TS0 R/W 0000H

F01B3H – – –

F01B4H Timer channel stop register 0 TT0L TT0 R/W 0000H

F01B5H – – –

F01B6H Timer clock select register 0 TPS0 R/W – – 0000H

F01B7H

F01B8H Timer output register 0 TO0L TO0 R/W – 0000H

F01B9H – – –

F01BAH Timer output enable register 0 TOE0L TOE0 R/W 0000H

F01BBH – – –

F01BCH Timer output level register 0 TOL0L TOL0 R/W – 0000H

F01BDH – – –

F01BEH Timer output mode register 0 TOM0L TOM0 R/W – 0000H

F01BFH – – –

F01C0H Timer counter register 10 TCR10 R – – FFFFH

F01C1H

F01C2H Timer counter register 11 TCR11 R – – FFFFH

F01C3H

F01C4H Timer counter register 12 TCR12 R – – FFFFH

F01C5H

Loading...

Loading...