RL78/F13, F14 CHAPTER 8 TIMER RD

R01UH0368EJ0210 Rev.2.10 601

Dec 10, 2015

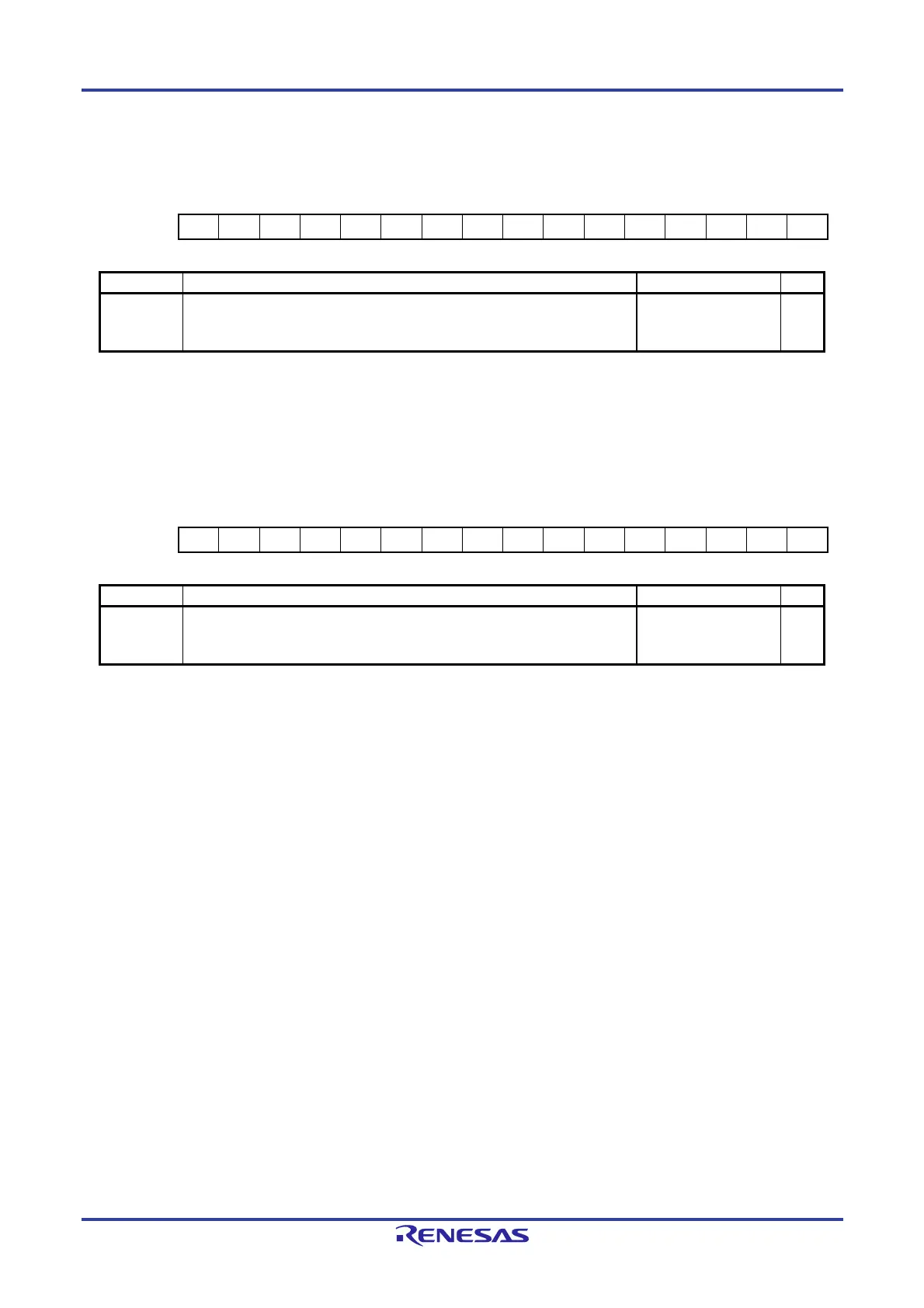

Figure 8-31. Format of Timer RD Counter i (TRDi) (i = 0 or 1) [Complementary PWM Mode (TRD0)]

Address: F0276H (TRD0), F0286H (TRD1) After Reset: 0000H

Note

Symbol 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TRDi

— — — — — — — — — — — — — — — —

— Function Setting Range R/W

Bits 15 to 0 Dead time must be set.

Count the count source. Count operation is incremented or decremented.

When an overflow occurs, the OVF bit in the TRDSR0 register is set to 1.

0001H to FFFFH R/W

Note The value after reset is undefined when FRQSEL4 = 1 in the user option byte (000C2H/020C2H) and TRD0EN =

0 in the PER1 register. If it is necessary to read the initial value, set fCLK to fIH and TRD0EN = 1 before reading.

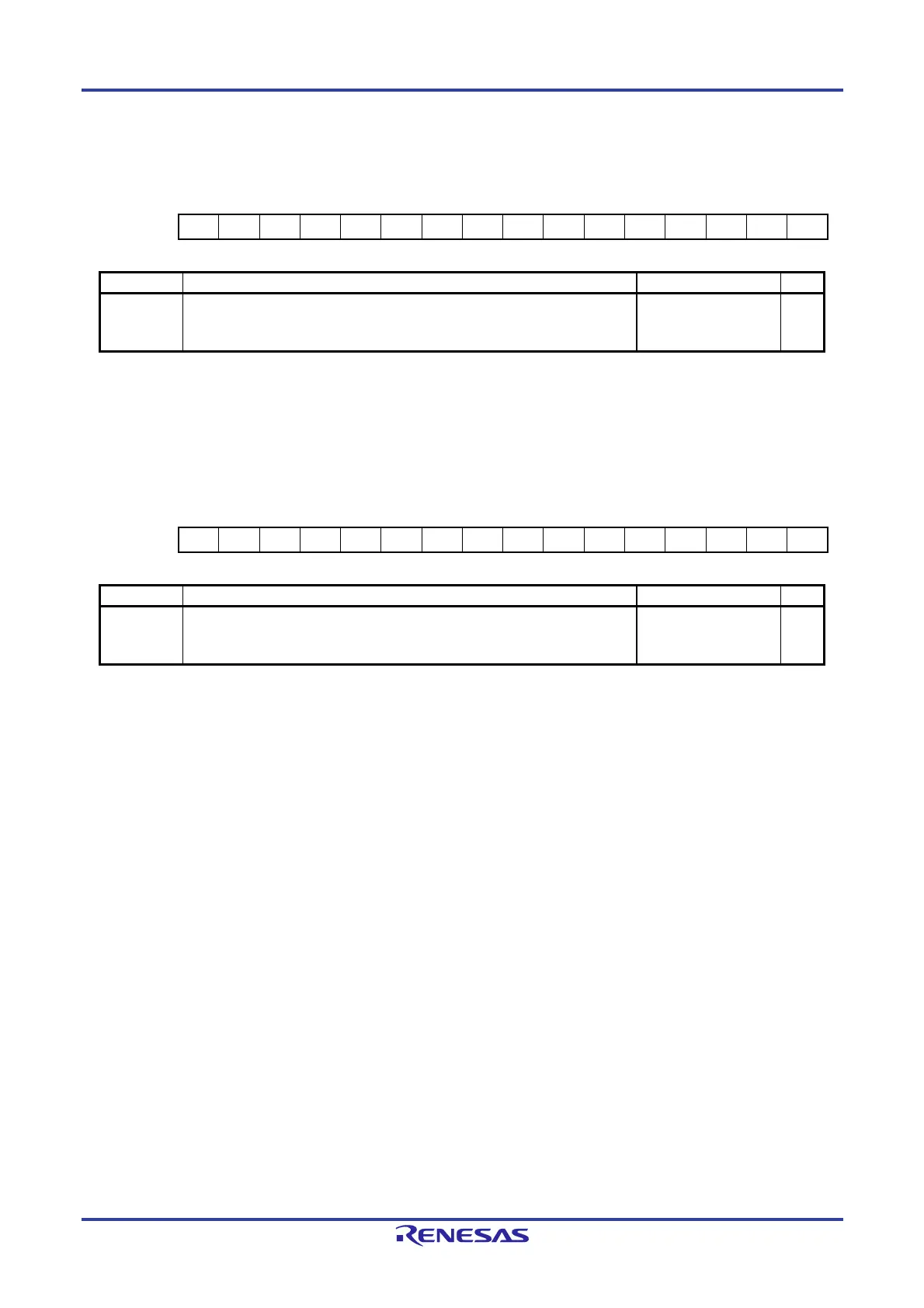

Figure 8-32. Format of Timer RD Counter i (TRDi) (i = 0 or 1) [Complementary PWM Mode (TRD1)]

Address: F0276H (TRD0), F0286H (TRD1) After Reset: 0000H

Note

Symbol 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TRDi

— — — — — — — — — — — — — — — —

— Function Setting Range R/W

Bits 15 to 0 Set to 0000H.

Count the count source. Count operation is incremented or decremented.

When an underflow occurs, the UDF bit in the TRDSR1 register is set to 1.

0000H to FFFFH R/W

Note The value after reset is undefined when FRQSEL4 = 1 in the user option byte (000C2H/020C2H) and TRD0EN =

0 in the PER1 register. If it is necessary to read the initial value, set fCLK to fIH and TRD0EN = 1 before reading.

Loading...

Loading...