RL78/F13, F14 CHAPTER 8 TIMER RD

R01UH0368EJ0210 Rev.2.10 621

Dec 10, 2015

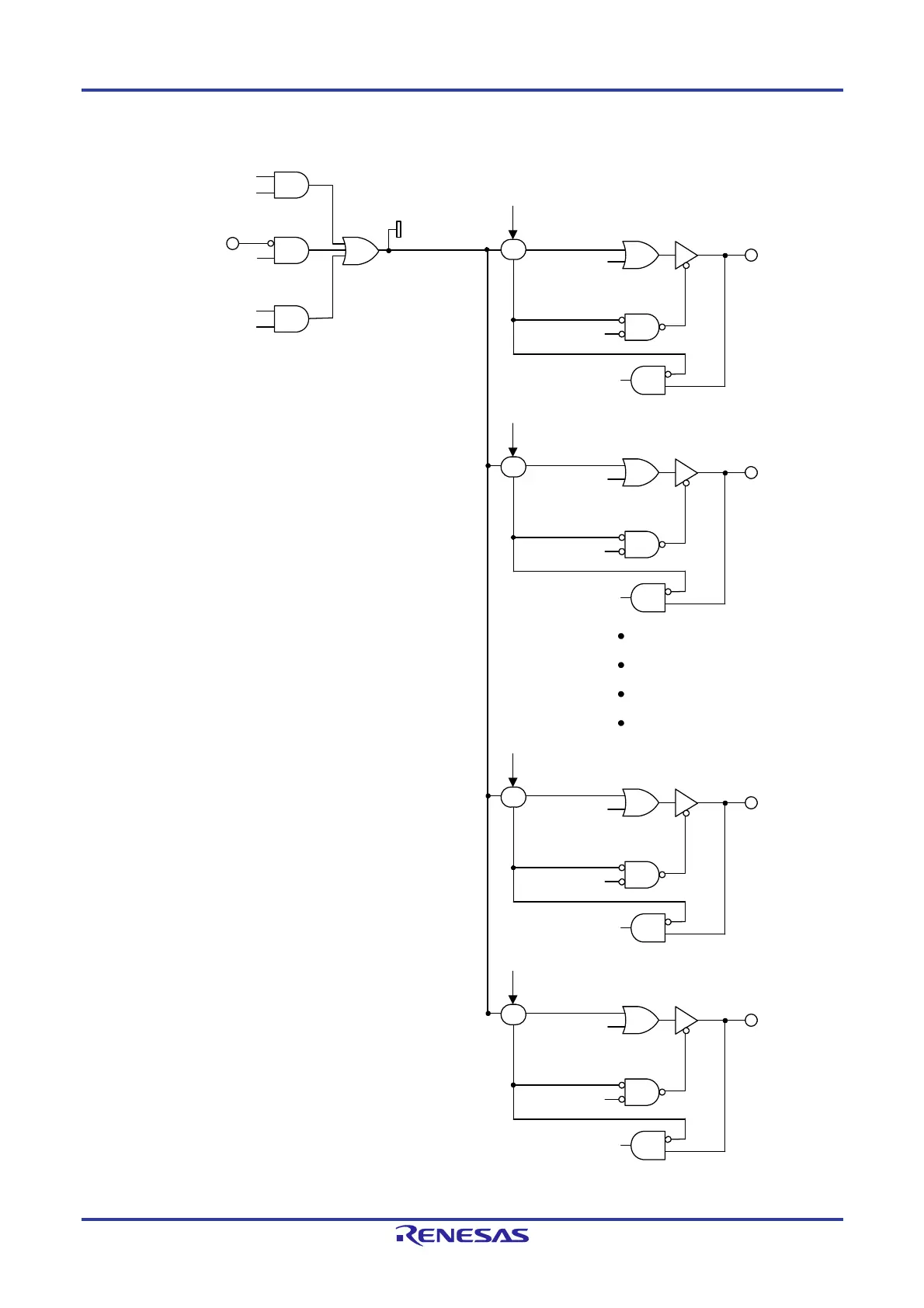

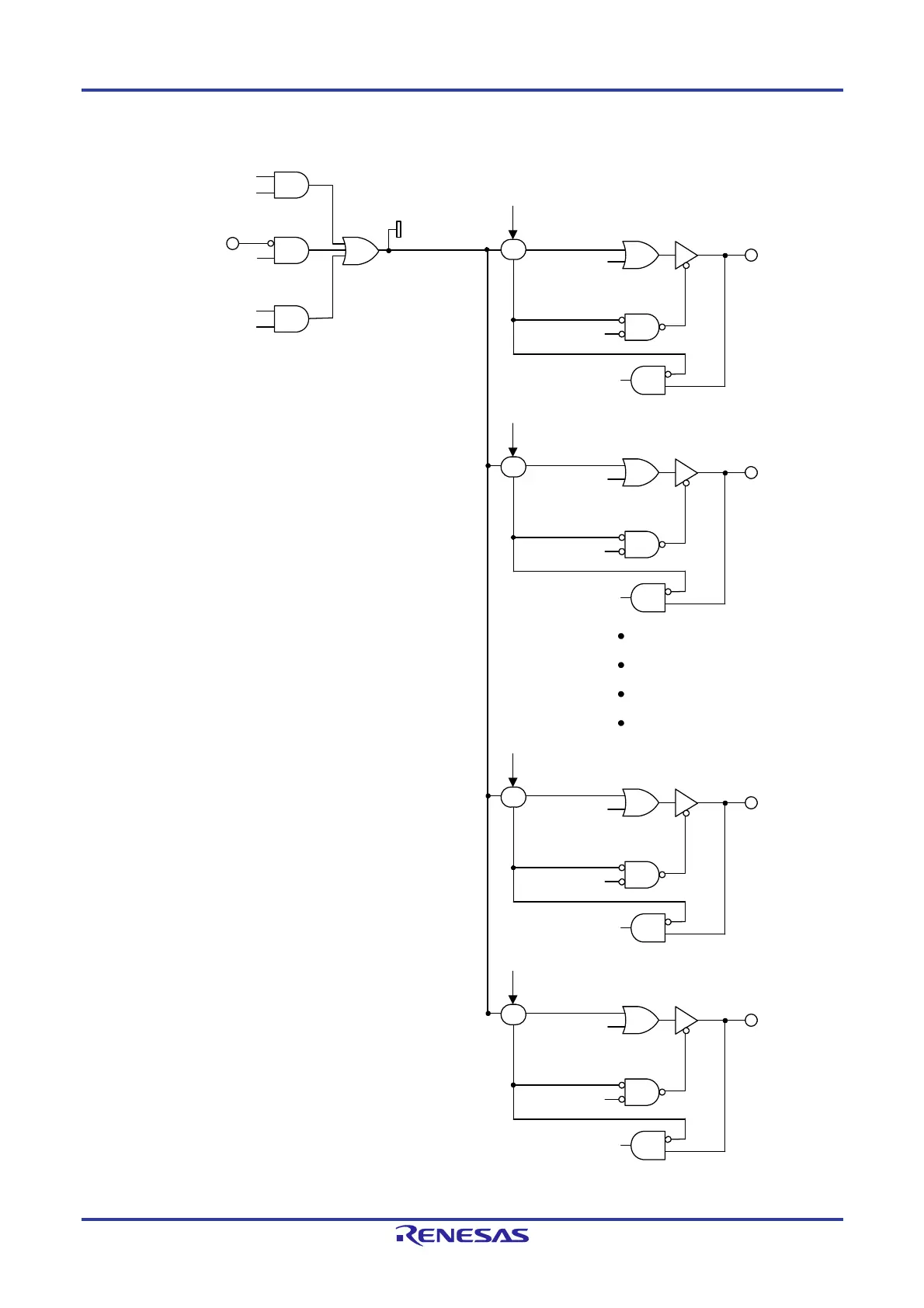

Figure 8-44. Pulse Output Forced Cutoff

INTP0 input

ELCOBE0, ELCOBE1: Bits in TRDELC register

TRDPTO, TRDSHUTS: Bits in TRDOER2 register

PM13, PM16, PM30, PM125: Bits in PM1, PM3, and PM12 register

DFCK1, DFCK0, PENB1, PENB0,

DFD, DFC, DFB, DFA: Bits in TRDDF0, and TRDDF1 register

TRDPTO

Event input 0 from ELC

ELCOBE0

Event input 1 from ELC

ELCOBE1

TRDSHUTS bit

TRDIOA0

Output data of

alternate I/O port

DFCK1, DFCK0

Hi-Z selection signal

PM13

Timer RD

output data

Input data

TRDIOB0

PENB1, PENB0

Hi-Z selection signal

PM125

Timer RD

output data

Input data

TRDIOC1

DFD, DFC

Hi-Z selection signal

PM16

Timer RD

output data

Input data

TRDIOD1

DFB, DFA

Hi-Z selection signal

PM30

Timer RD

output data

Input data

Output data of

alternate I/O port

Output data of

alternate I/O port

Output data of

alternate I/O port

<R>

Loading...

Loading...