1. Select basic (single width) in the RX rate match FIFO mode list.

2. Enter values for the following parameters.

Parameter Value Description

RX rate match insert/delete +ve

pattern (hex)

20 bits of data specified

as a hexadecimal string

The first 10 bits correspond to the skip pattern and the

last 10 bits correspond to the control pattern. The skip

pattern must have neutral disparity.

RX rate match insert/delete –ve

pattern (hex)

20 bits of data specified

as a hexadecimal string

The first 10 bits correspond to the skip pattern and the

last 10 bits correspond to the control pattern. The skip

pattern must have neutral disparity.

ve (volt encodes) are NRZ_L conditions where +ve encodes 0 and –ve encodes 1.

ve is a running disparity (+/–RD) specifically used with the rate matcher.

Depending on the ppm difference (which is defined by protocol) between the

recovered clock and the local clock, the rate matcher adds or deletes a maximum

of four skip patterns (neutral disparity). The net neutrality is conserved even after

the skip word insertion or deletion because the control words alternate between

positive and negative disparity.

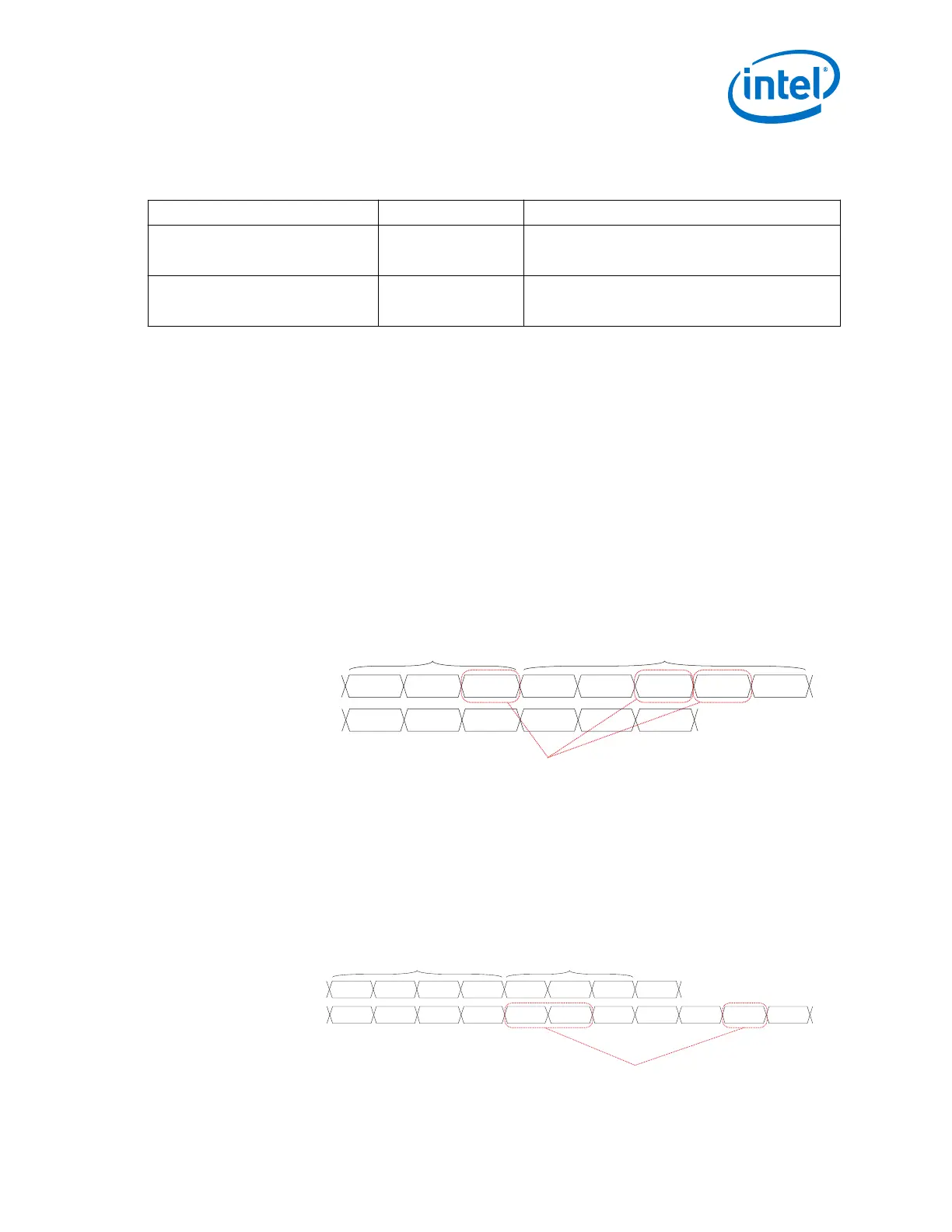

In the following figure, the first skip cluster has a /K28.5/ control pattern followed

by two /K28.0/ skip patterns. The second skip cluster has a /K28.5/ control

pattern followed by four /K28.0/ skip patterns. The rate match FIFO deletes only

one /K28.0/ skip pattern from the first skip cluster to maintain at least one skip

pattern in the cluster after deletion. Two /K28.0/ skip patterns are deleted from

the second cluster for a total of three skip patterns deletion requirement.

The rate match FIFO can insert a maximum of four skip patterns in a cluster, if

there are no more than five skip patterns in the cluster after insertion.

Figure 144. Rate Match FIFO Deletion with Three Skip Patterns Required for Deletion

tx_parallel_data

rx_parallel_data

First Skip Cluster

Second Skip Cluster

Three Skip Patterns Deleted

K28.5 K28.0 K28.0 K28.5 K28.0 K28.0 K28.0 K28.0

K28.5 K28.0 K28.5 K28.0 K28.0 K28.0

Note: /K28.5/ is the control pattern and /K28.0/ is the skip pattern

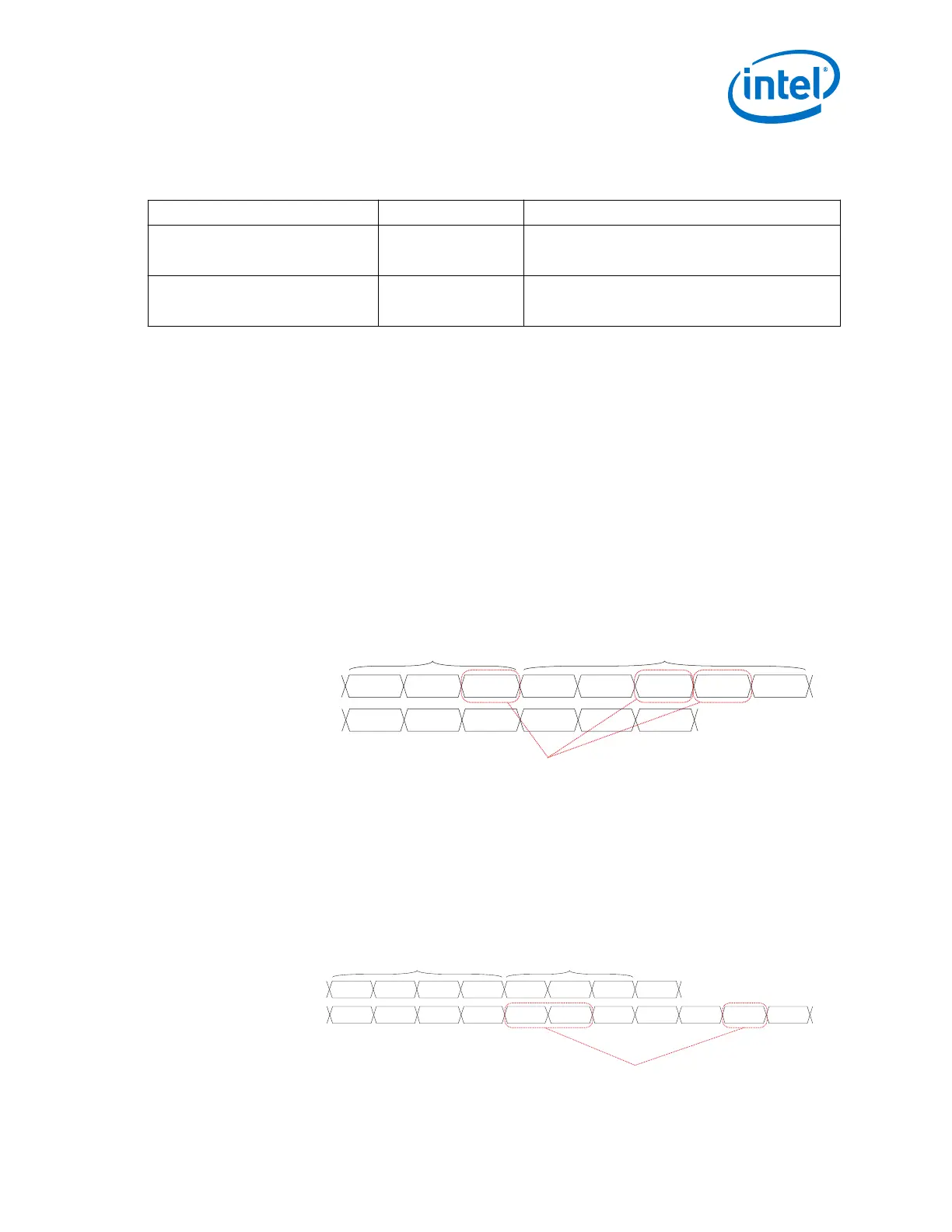

In the following figure, /K28.5/ is the control pattern and neutral disparity /K28.0/

is the skip pattern. The first skip cluster has a /K28.5/ control pattern followed by

three /K28.0/ skip patterns. The second skip cluster has a /K28.5/ control pattern

followed by two /K28.0/ skip patterns. The rate match FIFO inserts only two /

K28.0/ skip patterns into the first skip cluster to maintain a maximum of five skip

patterns in the cluster after insertion. One /K28.0/ skip pattern is inserted into the

second cluster for a total of three skip patterns to meet the insertion requirement.

Figure 145. Rate Match FIFO Insertion with Three Skip Patterns Required for Insertion

tx_parallel_data

rx_parallel_data

First Skip Cluster

Second Skip Cluster

Three Skip Patterns Inserted

K28.5 K28.0 K28.0 K28.0 K28.5 K28.0 K28.0 Dx.y

K28.5 K28.0 K28.0 K28.0 K28.0 K28.0

K28.5 K28.0 K28.0 K28.0 Dx.y

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

307

Loading...

Loading...