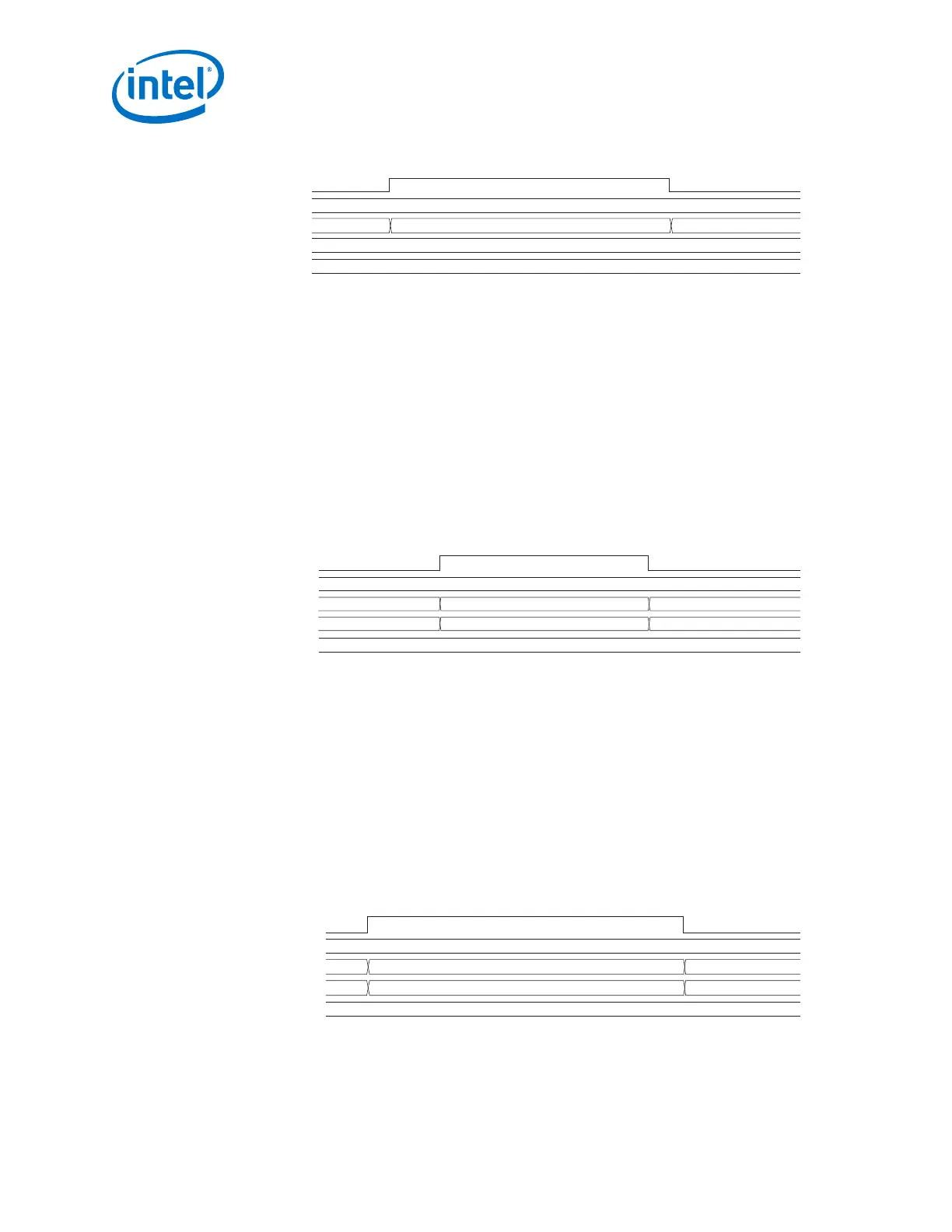

Figure 141. RX Polarity Inversion

tx_parallel_data

rx_parallel_data

11111100001110111100

11111100001... 00000011110001000011

01

11

11111100001110111100

rx_polinv

rx_patterndetect

rx_syncstatus

2.9.2.5. RX Bit Reversal

The RX bit reversal feature can be enabled in low latency, basic, and basic rate match

mode. The word aligner is available in any mode, bit slip, manual, or synchronous

state machine.

To enable this feature, select the Enable RX bit reversal and Enable

rx_std_bitrev_ena port options. This adds rx_std_bitrev_ena. If there is more

than one channel in the design, rx_std_bitrev_ena becomes a bus in which each

bit corresponds to a channel. As long as rx_std_bitrev_ena is asserted, the RX

data received by the core shows bit reversal.

You can verify this feature by monitoring rx_parallel_data.

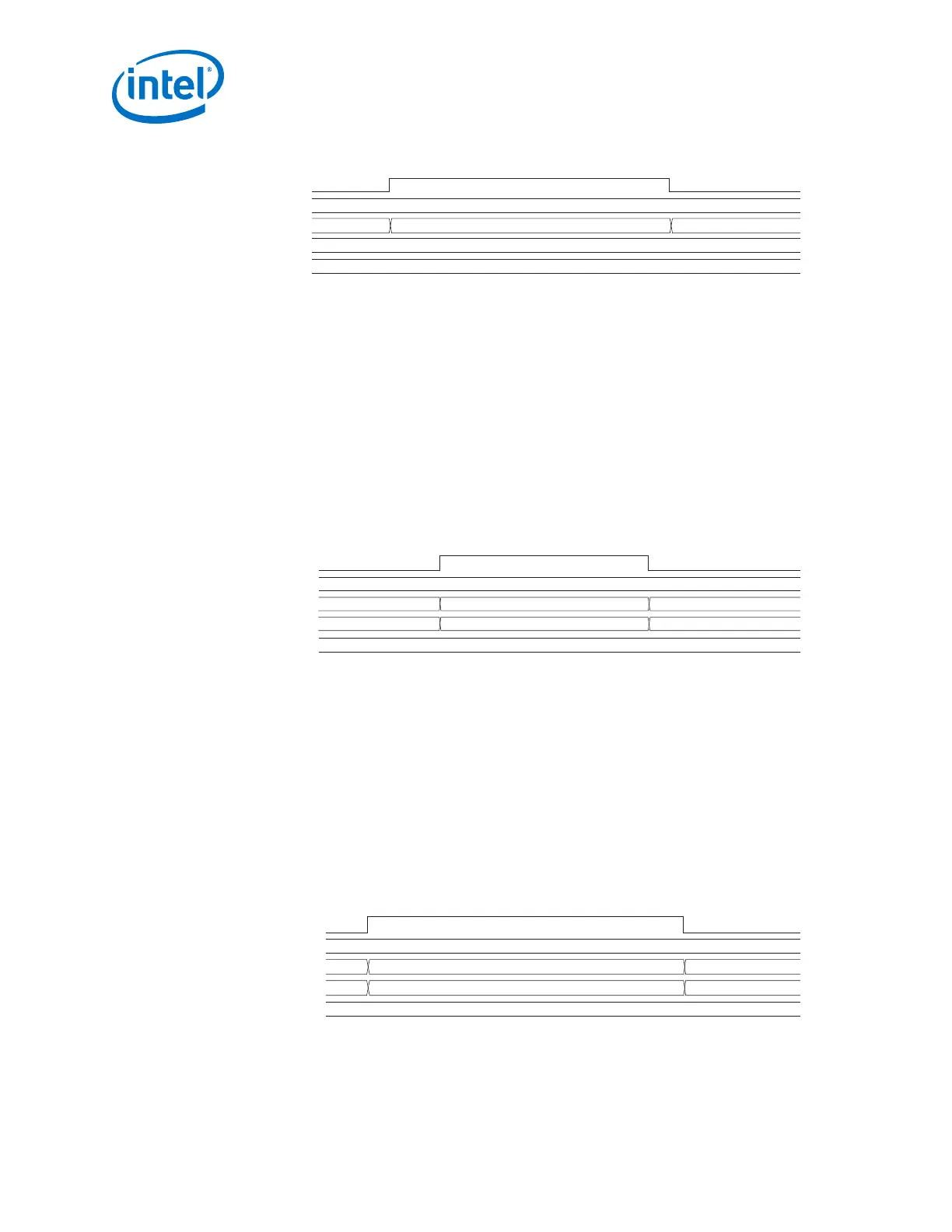

Figure 142. RX Bit Reversal

tx_parallel_data

rx_parallel_data

11111100001110111100

01

11

rx_std_bitrev_ena

rx_patterndetect

rx_syncstatus

00 01

11111100001110111100

1111110000111011110000111101110000111111

2.9.2.6. RX Byte Reversal

The RX byte reversal feature can be enabled in low latency, basic, and basic rate

match mode. The word aligner is available in any mode.

To enable this feature, select the Enable RX byte reversal and Enable

rx_std_byterev_ena port options. This adds rx_std_byterev_ena. If there is

more than one channel in the design, rx_std_byterev_ena becomes a bus in which

each bit corresponds to a channel. As long as rx_std_byterev_ena is asserted, the

RX data received by the core shows byte reversal.

You can verify this feature by monitoring rx_parallel_data.

Figure 143. RX Byte Reversal

tx_parallel_data

rx_parallel_data

11111100001110111100

01

11

rx_std_byterev_ena

rx_patterndetect

rx_syncstatus

01

111111... 11111100001110111100

10

11101111001111110000

2.9.2.7. Rate Match FIFO in Basic (Single Width) Mode

Only the rate match FIFO operation is covered in these steps.

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

306

Loading...

Loading...