Depending on your PCS-PMA interface width, the word aligner can be configured in

one of the following modes:

• Bit slip

• Manual alignment

• Synchronous state machine

• Deterministic latency

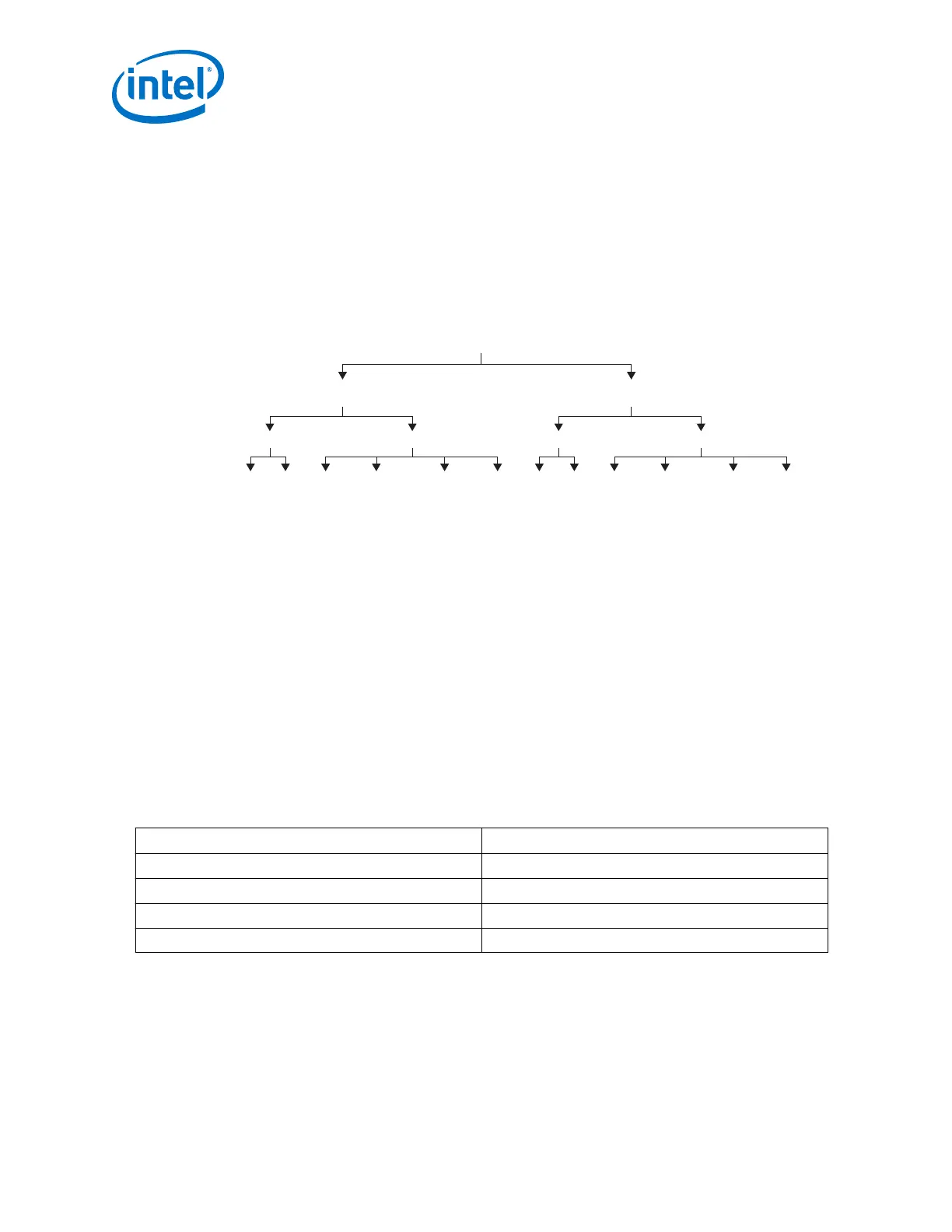

Figure 259. Word Aligner Conditions and Modes

Word

Aligner

Single

Width

Double

Width

8 Bit

Bit Slip Manual

10 Bit

Bit Slip ManualDeterministic

Latency (1)

Synchronous

State Machine

16 Bit

Bit Slip Manual

20 Bit

Bit Slip ManualDeterministic

Latency (1)

Synchronous

State Machine

Note:

1. This option is available in CPRI mode.

5.3.2.1.1. Word Aligner Bit Slip Mode

In bit slip mode, the word aligner operation is controlled by rx_bitslip, which has

to be held for two parallel clock cycles. At every rising edge of rx_bitslip, the bit

slip circuitry slips one bit into the received data stream, effectively shifting the word

boundary by one bit. Pattern detection is not used in bit slipping mode; therefore,

rx_syncstatus is not valid in this mode.

5.3.2.1.2. Word Aligner Manual Mode

In manual alignment mode, the word aligner operation is controlled by

rx_std_wa_patternalign. The word aligner operation is edge-sensitive or level-

sensitive to rx_std_wa_patternalign, depending upon the PCS-PMA interface

width selected.

Table 259.

Word Aligner rx_std_wa_patternalign Behavior

PCS-PMA Interface Width

rx_std_wa_patternalign Behavior

8 Rising edge sensitive

10 Level sensitive

16 Rising edge sensitive

20 Rising edge sensitive

If rx_std_wa_patternalign is asserted, the word aligner looks for the

programmed word alignment pattern in the received data stream. It updates the word

boundary if it finds the word alignment pattern in a new word boundary. If

rx_std_wa_patternalign is deasserted, the word aligner maintains the current

word boundary even when it sees the word alignment pattern in a new word

boundary.

5. Arria 10 Transceiver PHY Architecture

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

486

Loading...

Loading...