1. Perform the necessary steps from steps 1 to 7 in Steps to Perform Dynamic

Reconfiguration.

2. Perform a read-modify-write to address 0x00A with a value of 1'b1 to bit[7].

3. Perform a read-modify-write to address 0x00B according to Register Map for PRBS

Checker for bonded and non bonded designs.

4. Perform a read-modify-write to address 0x00C according to Register Map for PRBS

Checker for bonded and non bonded designs.

5. Perform a read-modify-write to address 0x13F according to Register Map for PRBS

Checker for bonded and non bonded designs.

6. Perform a read-modify-write to address 0x111 according to Register Map for PRBS

Checker for bonded and non bonded designs.

7. Perform the necessary steps from steps 9 to 12 in Steps to Perform Dynamic

Reconfiguration.

To disable the PRBS verifier write the original values back into the read-modify-

write addresses listed above.

6.16.1.5. Disabling/Enabling PRBS Pattern Inversion

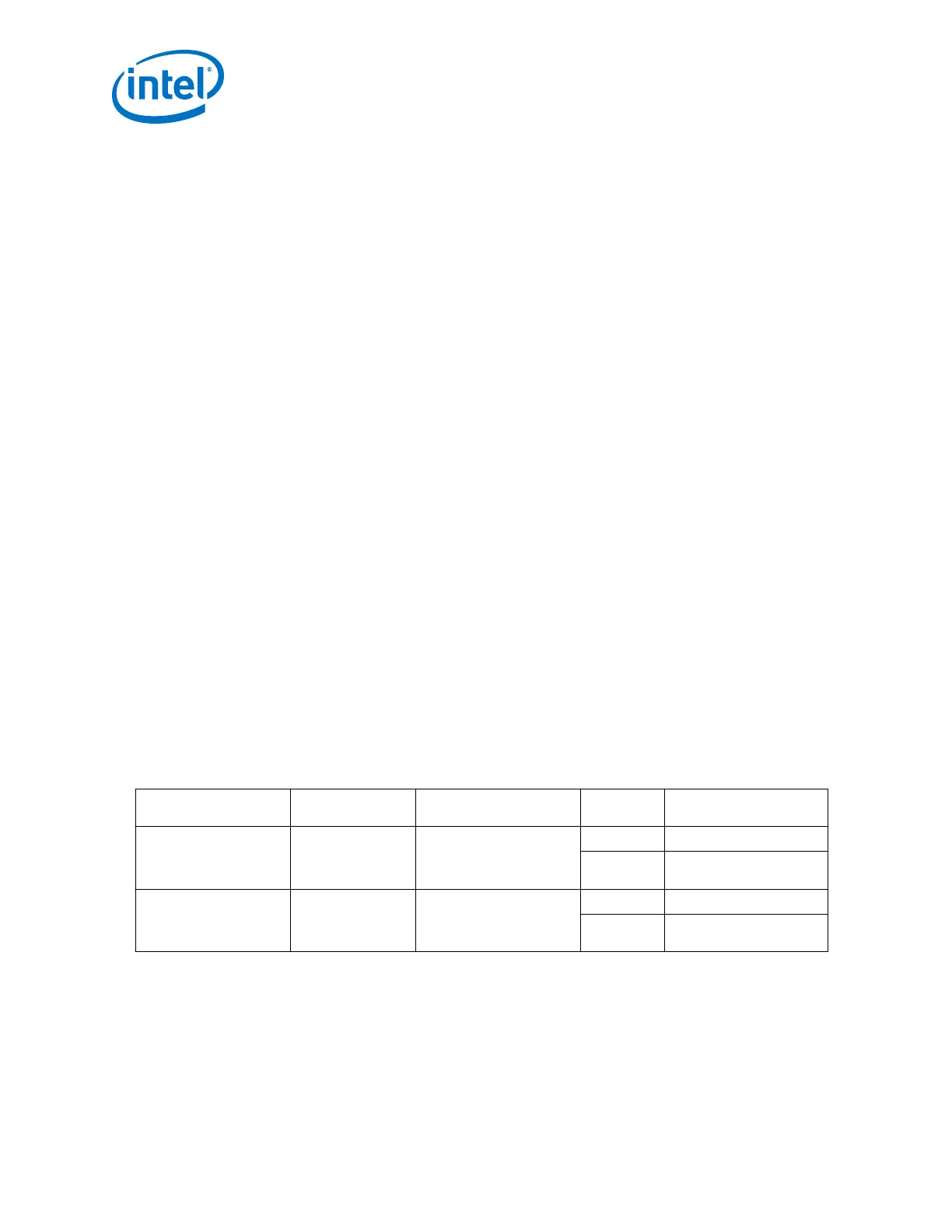

The default PRBS pattern is inverted for both the PRBS generator and checker. You can

disable pattern inversion for PRBS data leaving or entering the PRBS data pattern

generator and checker, respectively. Table 294 on page 558 shows the addresses and

bits to control the inversion of the PRBS generator or checker. To disable the PRBS

pattern inversion for the PRBS generator or checker, follow these steps:

1. Perform the necessary steps from steps 1 to 7 in Steps to Perform Dynamic

Reconfiguration.

2. To disable the inverted PRBS pattern leaving the PRBS generator, perform a read-

modify-write to bit[2] with a value of 1'b1 to address 0x7.

3. To disable the inverted PRBS pattern entering the PRBS checker, perform a read-

modify-write to bit[4] with a value of 1'b1 to address 0xA.

4. Perform the necessary steps from steps 9 to 12 in Steps to Perform Dynamic

Reconfiguration.

Table 294. Register Map for PRBS Pattern Inversion

Reconfiguration

Address (HEX)

Reconfiguration Bit Attribute Name Bit Encoding Description

0x7 [2] tx_static_polarity_inversion 1'b1 Disables PRBS inversion

1'b0 Enables PRBS inversion

(default)

0xA [4] rx_static_polarity_inversion 1'b1 Disables PRBS inversion

1'b0 Enables PRBS inversion

(default)

Related Information

Steps to Perform Dynamic Reconfiguration on page 516

6. Reconfiguration Interface and Dynamic Reconfiguration

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

558

Loading...

Loading...