RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1178

Dec 10, 2015

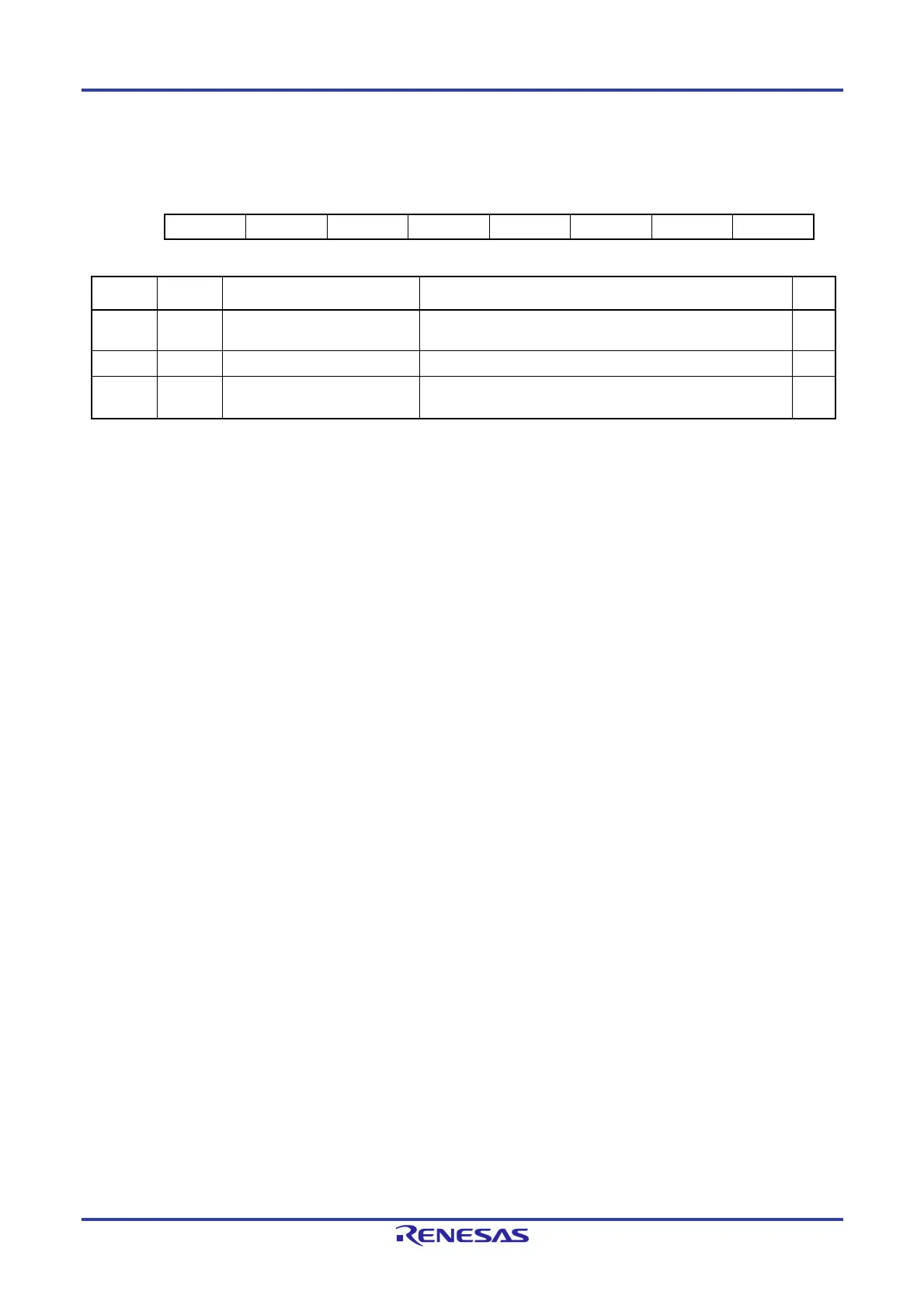

(13) LIN/UART Control Register (LCUCn)

Address: F06CEH

7 6 5 4 3 2 1 0

— — — — — — — OM0

Value after reset:

0 0 0 0 0 0 0 0

Bit Symbol Bit Name Function R/W

0 OM0 LIN Reset 0: LIN reset mode is caused.

1: LIN reset mode is canceled.

R/W

1 — Reserved This bit is always read as 0. The write value should always be 0. R/W

7 to 2 — Reserved These bits are always read as 0. The write value should always

be 0.

R/W

After a value is written to this register, confirm that the value written is actually indicated in the LMSTn register before writing

another value.

OM0 bit (LIN reset bit)

The OM0 bit selects either causing a transition to LIN reset mode or canceling LIN reset mode.

With 0 set, LIN reset mode is caused.

With 1 set, LIN reset mode is canceled.

Loading...

Loading...