RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1177

Dec 10, 2015

(12) LIN/UART Error Detection Enable Register (LEDEn)

Address: F06CDH

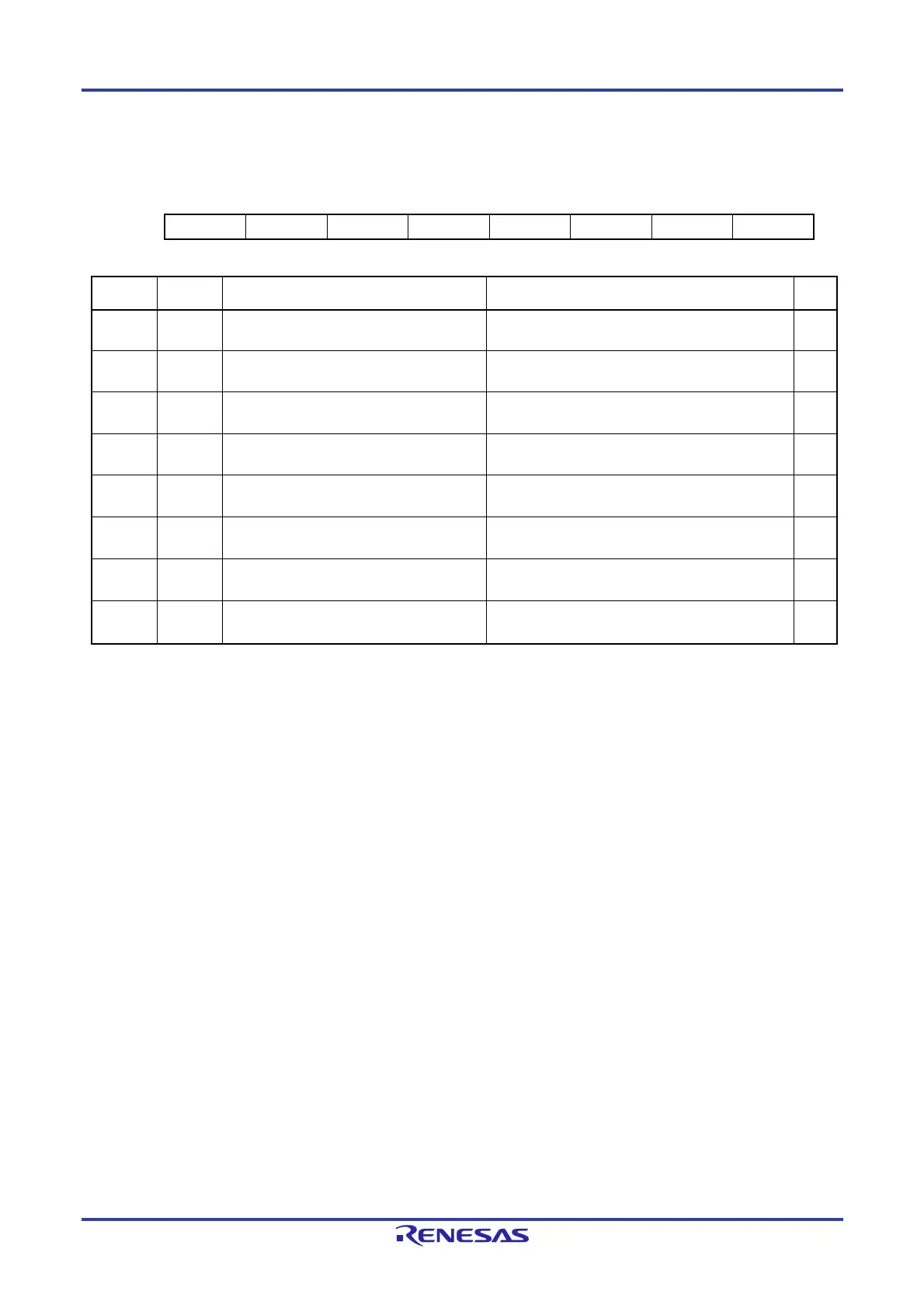

7 6 5 4 3 2 1 0

— — — — FERE OERE — BERE

Value after reset:

0 0 0 0 0 0 0 0

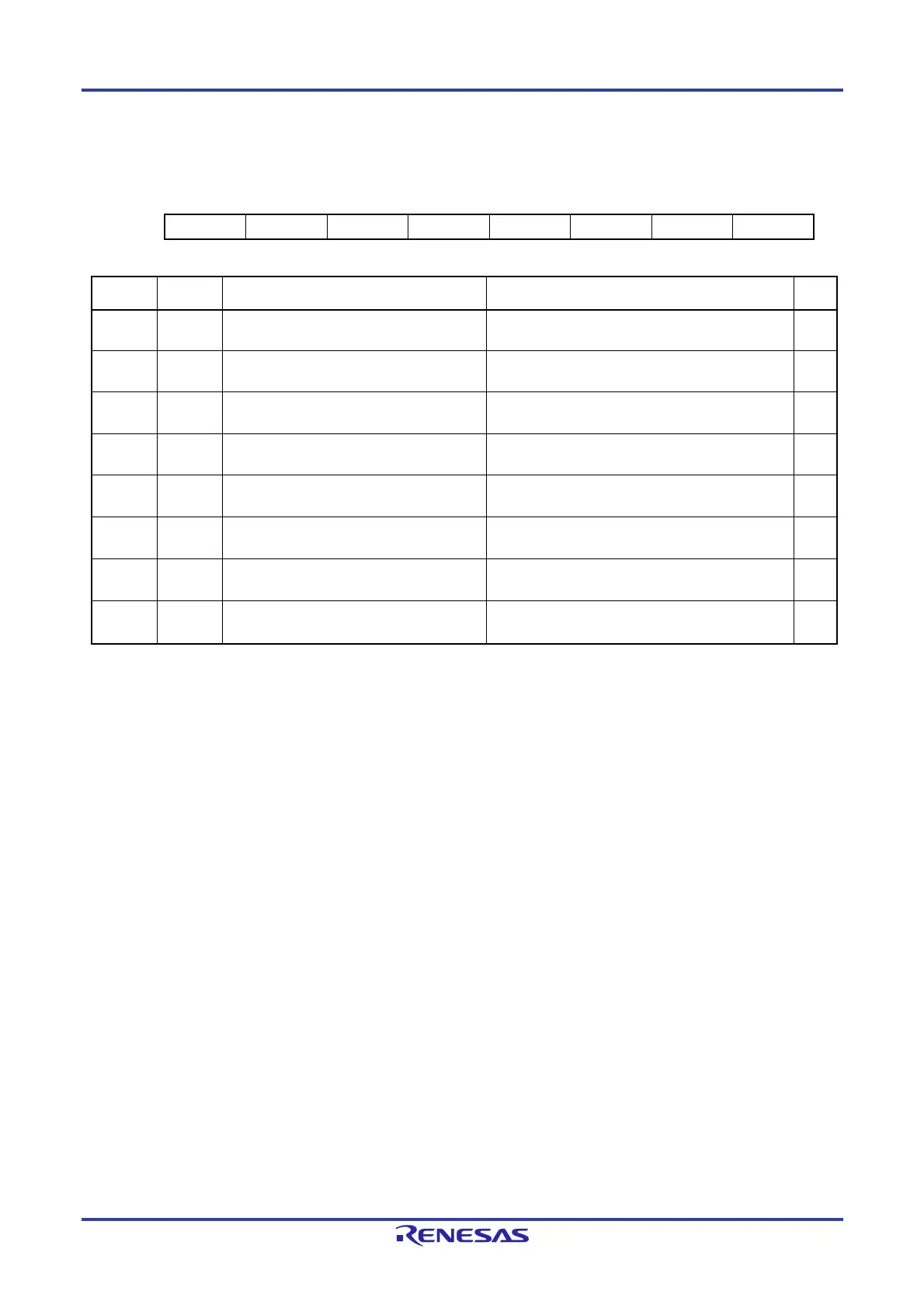

Bit Symbol Bit Name Function R/W

0 BERE Bit Error Detection Enable 0: Disables bit error detection.

1: Enables bit error detection.

R/W

1 — Reserved This bit is always read as 0. The write value should

always be 0.

R/W

2 OERE Overrun Error Detection Enable 0: Disables overrun error detection.

1: Enables overrun error detection.

R/W

3 FERE Framing Error Detection Enable 0: Disables framing error detection.

1: Enables framing error detection.

R/W

4 — Reserved This bit is always read as 0. The write value should

always be 0.

R/W

5 — Reserved This bit is always read as 0. The write value should

always be 0.

R/W

6 — Reserved This bit is always read as 0. The write value should

always be 0.

R/W

7 — Reserved This bit is always read as 0. The write value should

always be 0.

R/W

Set the LEDEn register when the OMM0 bit in the LMSTn register is 0 (LIN reset mode).

BERE bit (bit error detection enable bit)

The BERE bit enables or disables detection of the bit error.

With 0 set, the bit error is not detected.

With 1 set, the bit error is detected.

When this bit is set to 1, the detection result is indicated in the BER flag in the LESTn register.

Do not set this bit to 1 when the LIN/UART module is used in full-duplex mode.

For details of the bit error, refer to 17.5.5 Error Status.

Do not set this bit when the NSPB bits in the LWBRn register are 0101b (6 sampling) and the LRDNFS bit in the LMDn

register is 0 (the noise filter is in use).

OERE bit (overrun error detection enable bit)

The OERE bit enables or disables detection of the overrun error.

With 0 set, the overrun error is not detected.

With 1 set, the overrun error is detected.

When this bit is set to 1, the detection result is indicated in the OER flag in the LESTn register.

For details of the overrun error, refer to 17.5.5 Error Status.

FERE bit (framing error detection enable bit)

The FERE bit enables or disables detection of the framing error.

With 0 set, the framing error is not detected.

With 1 set, the framing error is detected.

When this bit is set to 1, the detection result is indicated in the FER flag in the LESTn register.

For details of the framing error, refer to 17.5.5 Error Status.

Loading...

Loading...