RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1227

Dec 10, 2015

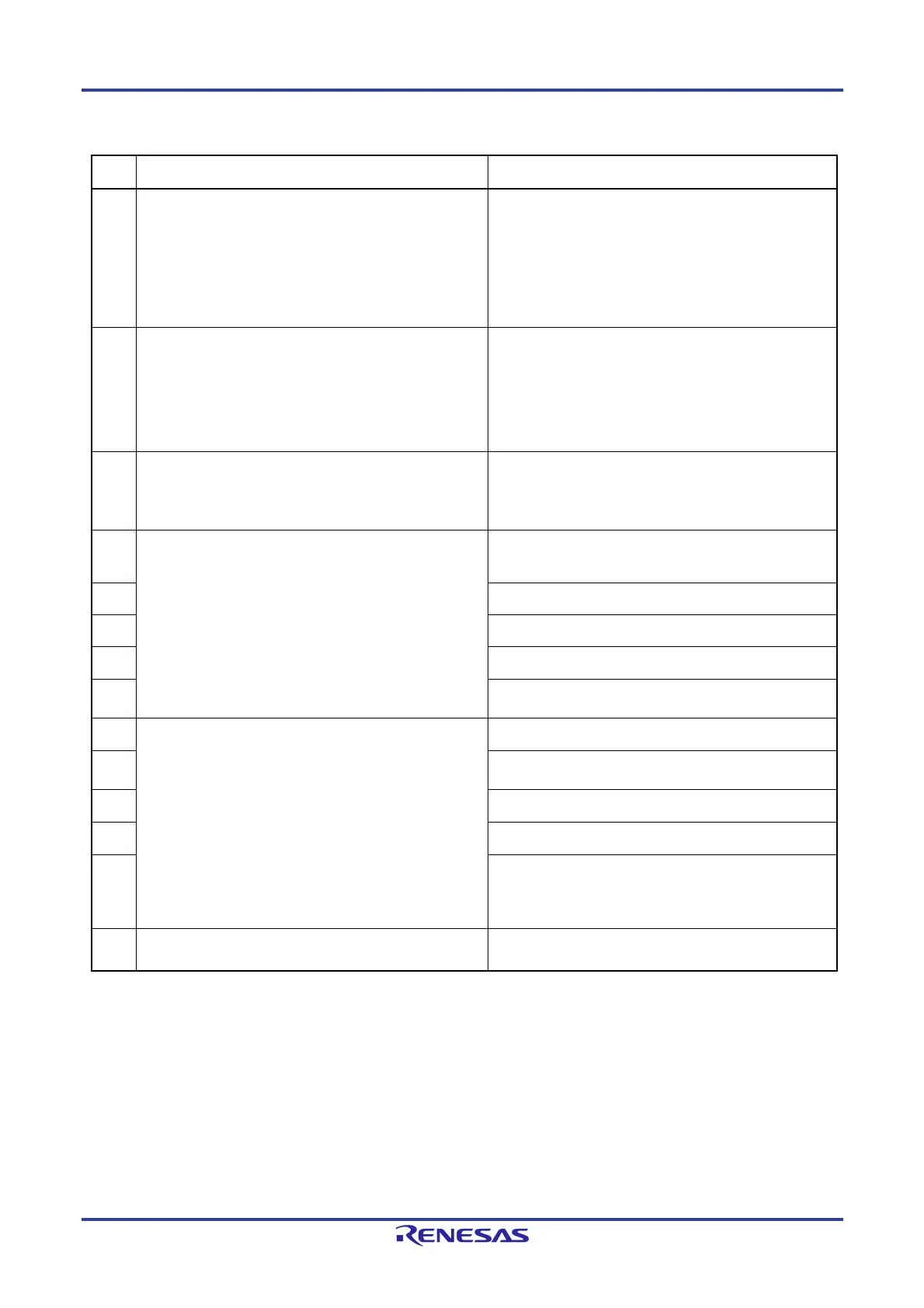

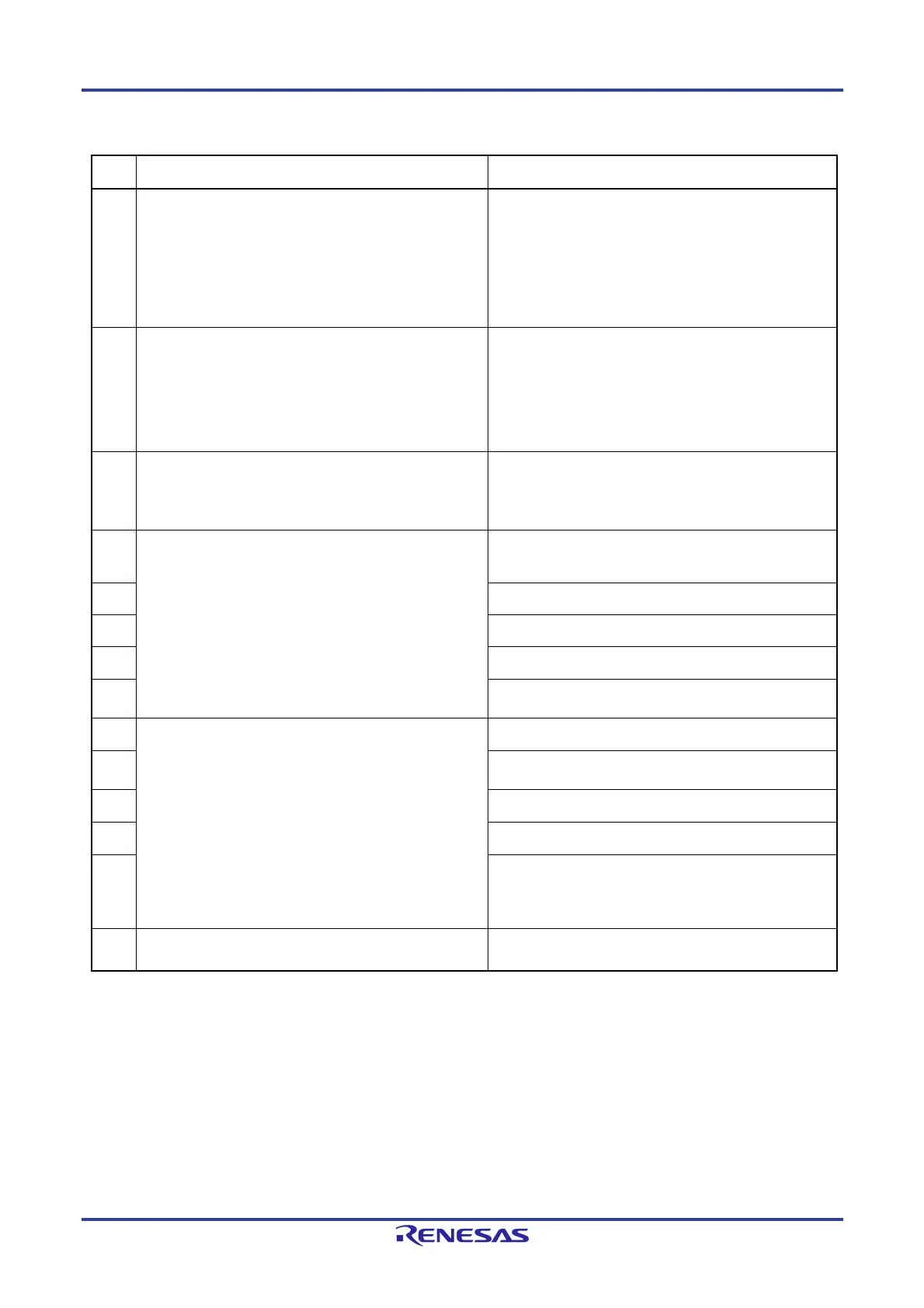

Table 17-19. UART Buffer Transmission Processing in LIN/UART Module (in UART mode)

Step Software processing LIN/UART module processing

(1)

Sets a baud rate.

Sets noise filter ON/OFF.

Sets error detection enable.

Sets data format.

Sets an interrupt generation timing to the end of

transmission.

Clears the LIN/UART module from LIN reset mode.

Sets the transmit enable bit (UTOE bit) to 1 Waits for a transmission trigger (RTS bit) by software.

(2)

Sets a UART buffer data length and whether the system

must wait for the start of transmission.

Sets the transmission data in the UART data buffer 0

register (LUDBn0) and the LIN/UART data buffer m

register (LDBnm).

Sets the UART buffer transmission start bit (RTS).

Sets the transmission status flag.

(3)

Waits for an interrupt request.

Transmits a start bit (for switching between transmission

and reception in half duplex communication, transmits a

start bit after receiving 1 stop bit. This function is referred to

in 17.5.1 (4) Transmission Start Wait Function).

(4) Transmits the data set in the UART data buffer 0 register

(LUDBn0) and the LIN/UART data buffer m register

(LDBnm).

(5) Transmits a parity bit when parity is used.

(6) Transmits 1 or 2 stop bits

(7) Transmits an inter-byte space (idle).

Repeats steps (3) to (7) until frame count -1 that was set in

the UART buffer data length select bits is reached.

(8) Transmits a start bit.

(9) Transmits the data set in the LIN/UART data buffer m

register (LDBnm).

(10) Transmits a parity bit when parity is used.

(11) Transmits 1 or 2 stop bits.

(12)

Sets the buffer transmission end flag.

Clears the UART buffer transmit start (RTS) bit.

Outputs a transmission interrupt.

Clears the transmission status flag.

(13)

Checks the LSTn register and clears flags

When transmitting data continuously, goes to step (2).

n = 0, 1

Loading...

Loading...