RL78/F13, F14 CHAPTER 23 STANDBY FUNCTION

R01UH0368EJ0210 Rev.2.10 1532

Dec 10, 2015

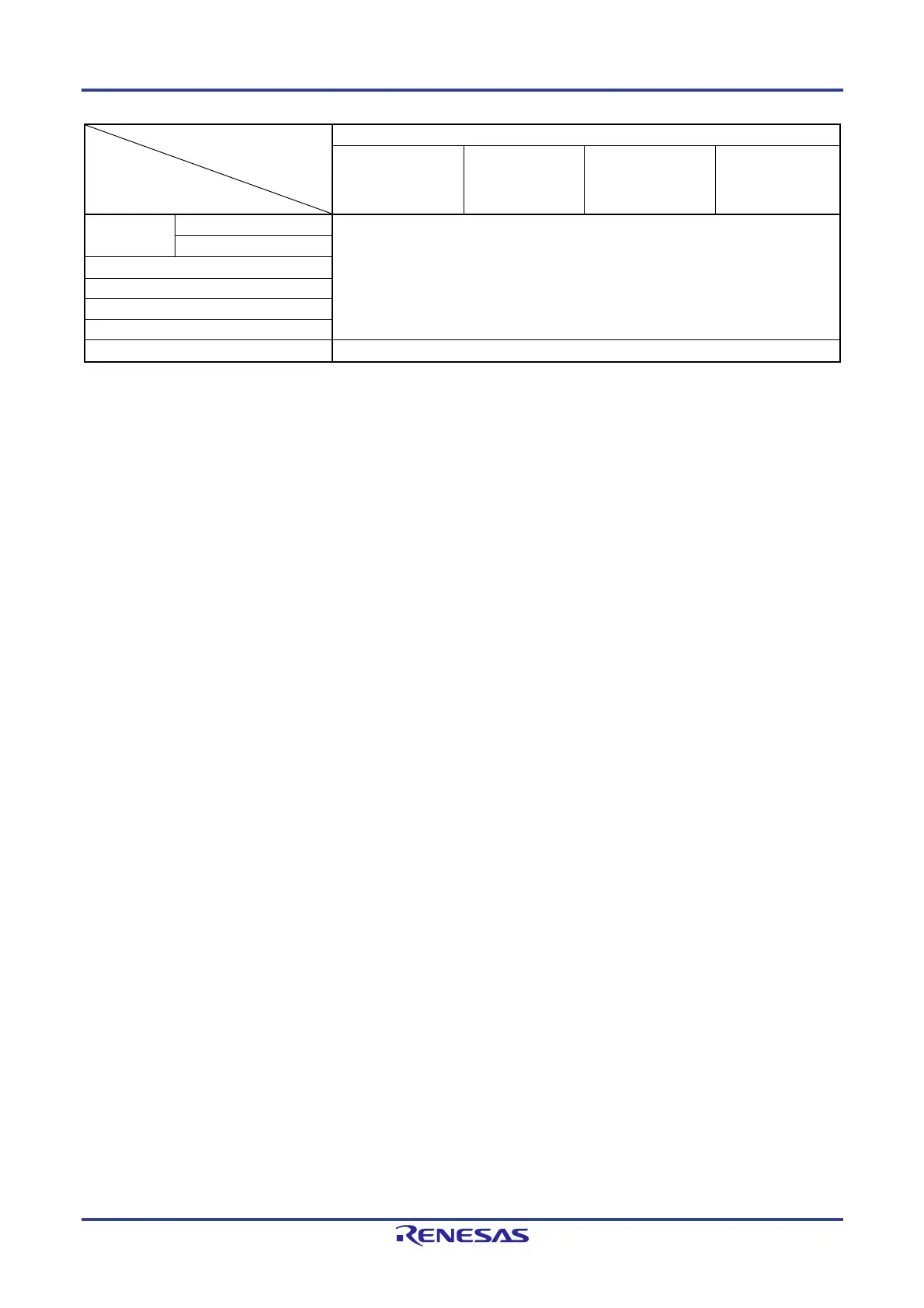

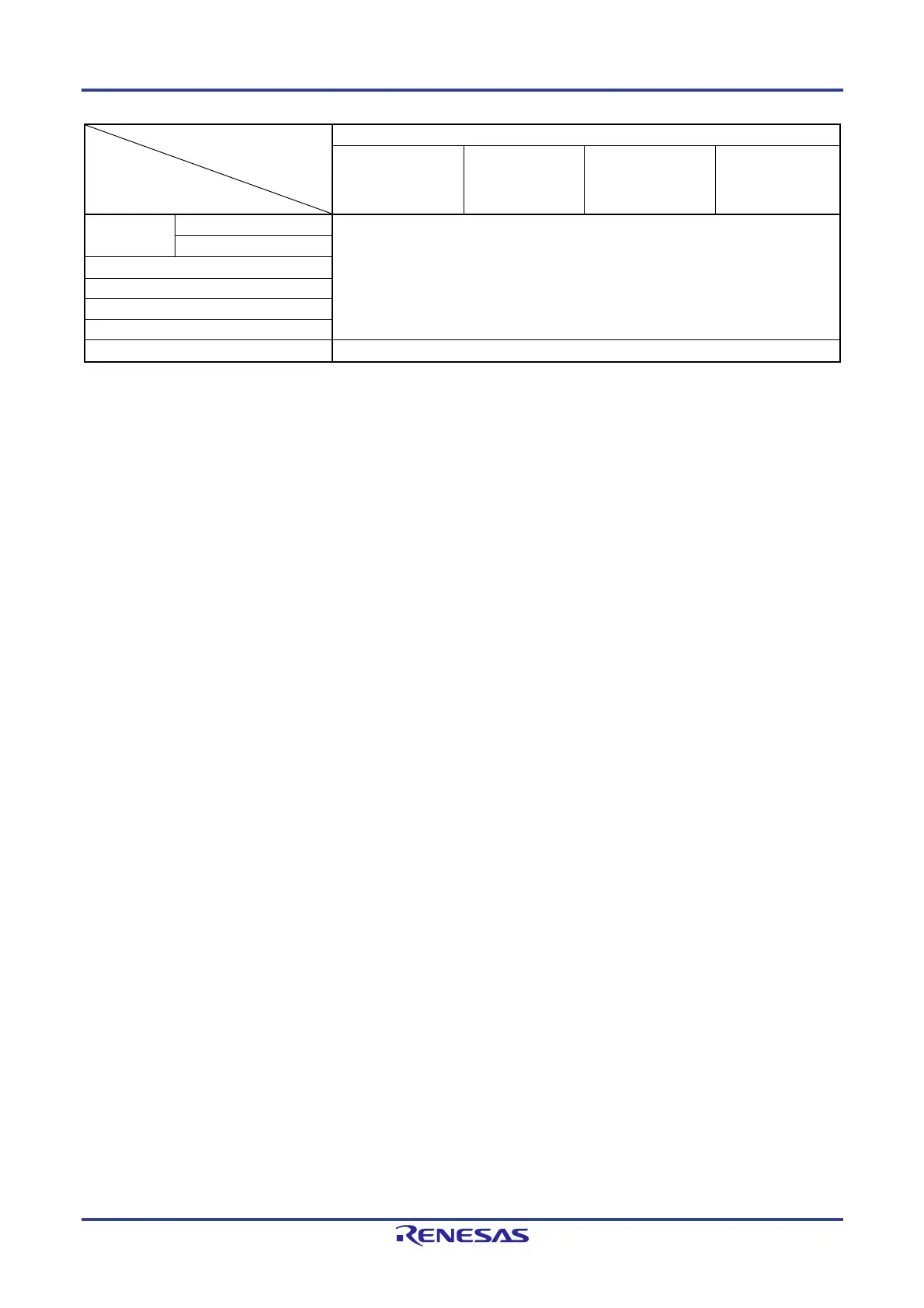

STOP Mode Setting

Item

When STOP Instruction Is Executed While CPU Is Operating on Main System Clock

When CPU Is

Operating on High-

speed On-chip

Oscillator clock (f

IH)

When CPU Is

Operating on X1

Clock (f

X)

When CPU Is

Operating on

External Main

System Clock (f

EX)

When CPU Is

Operating on PLL

Clock (f

PLL)

CRC operation

function

High-speed CRC Operation stopped

General-purpose CRC

Illegal-memory access detection function

RAM2 bit error detection function

RAM guard function

SFR guard function

CPU stack pointer monitor function

Operation stopped (operation can continue during vectored interrupt servicing)

Remark Operation stopped: Operation is automatically stopped before switching to the STOP mode.

Operation disabled: Operation is stopped before switching to the STOP mode.

fIH: High-speed on-chip oscillator clock fIL: Low-speed on-chip oscillator clock

f

X: X1 clock fEX: External main system clock

f

XT: XT1 clock fEXS: External subsystem clock

fPLL: PLL clock

f

WDT: WDT-dedicated low-speed on-chip oscillator clock

Cautions 1. To use the peripheral hardware that stops operation in the STOP mode, and the peripheral hardware

for which the clock that stops oscillating in the STOP mode after the STOP mode is released, restart

the peripheral hardware.

2. To stop the watchdog timer clock in the STOP mode, set bit 0 (WDSTBYON) of a user option byte

(000C0H/020C0H) to 0 (stop the watchdog timer operation in the HALT/STOP/SNOOZE mode).

3. To shorten oscillation stabilization time after the STOP mode is released when the CPU operates with

the high-speed system clock (X1 oscillation), temporarily switch the CPU clock to the high-speed on-

chip oscillator clock before the execution of the STOP instruction. Before changing the CPU clock

from the high-speed on-chip oscillator clock to the high-speed system clock (X1 oscillation) after the

STOP mode is released, check the oscillation stabilization time with the oscillation stabilization time

counter status register (OSTC).

Loading...

Loading...