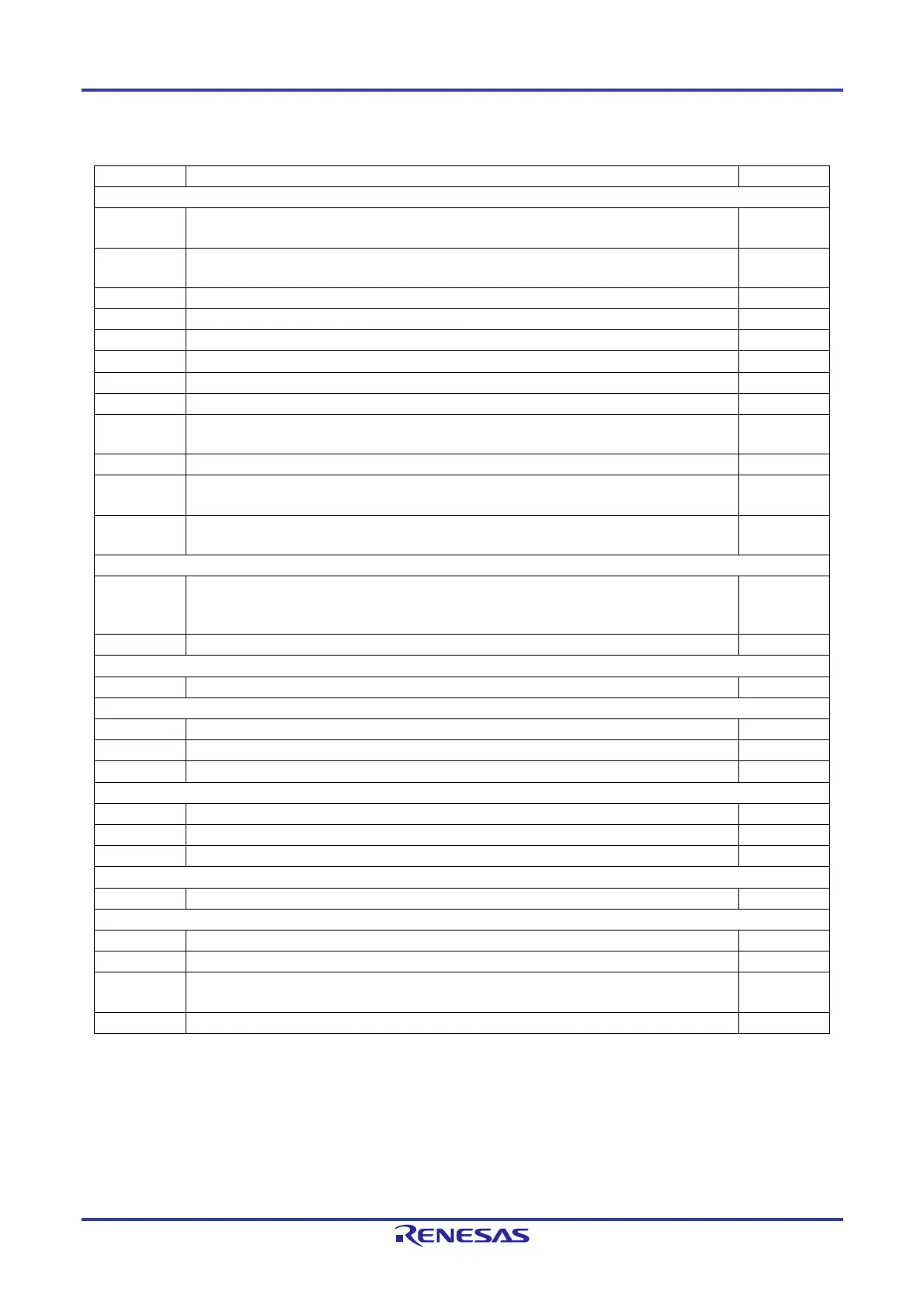

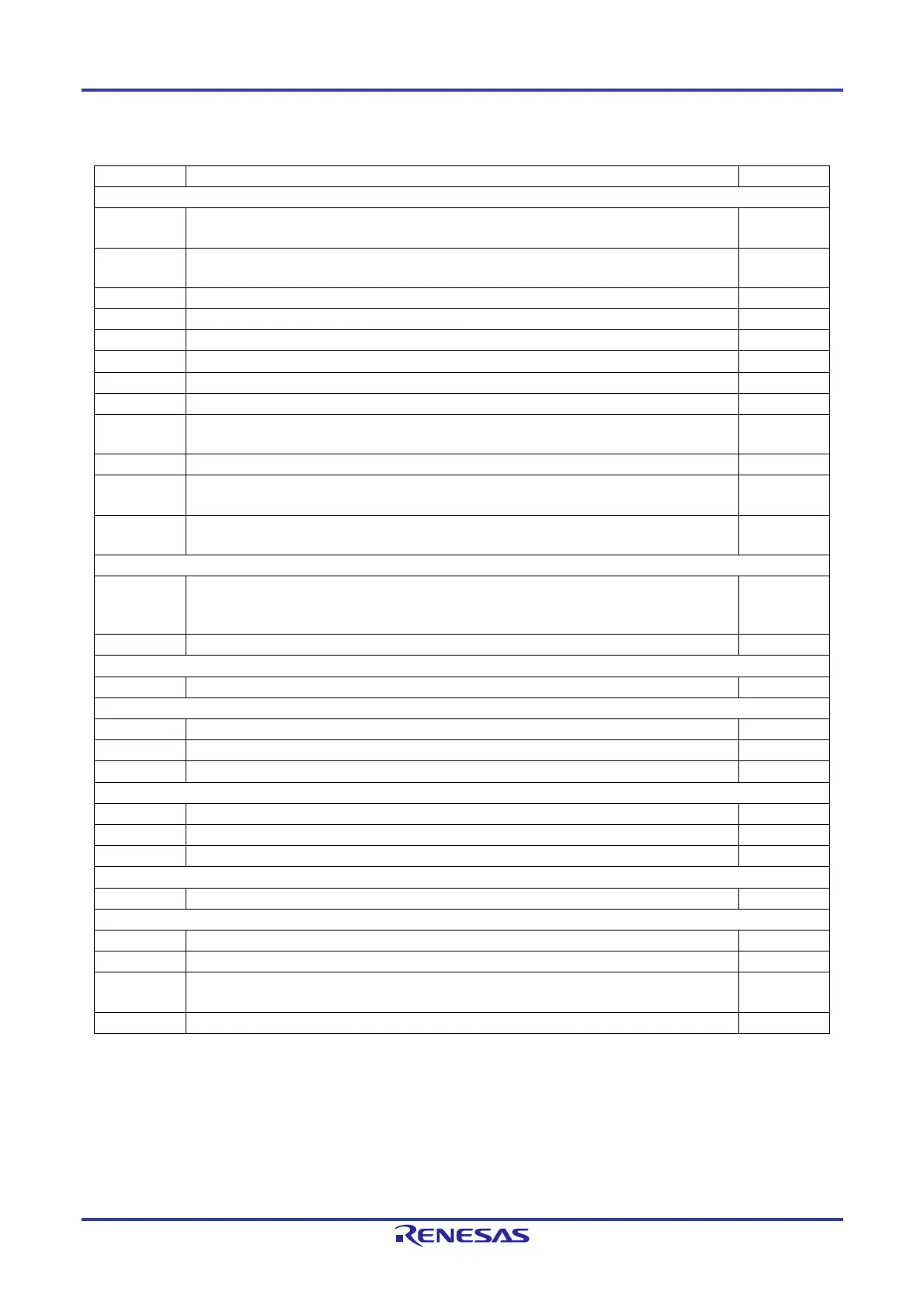

RL78/F13, F14 APPENDIX B REVISION HISTORY

R01UH0368EJ0210 Rev.2.10 1843

Dec 10, 2015

(2/3)

Page Description Classification

CHAPTER 17 LIN/UART MODULE (RLIN3)

p.1112,1140

,1168

LIN Clock Select Register (LINCKSEL), added Note of LINnMCK (c)

p.1123,1124

,1150

LIN/UART Error Detection Enable Register (LEDEn), added description of (Bit Error) and (Framing Error) (c)

p.1153 LIN/UART Transmission Control Register (LTRCn), deleted description of FTS bit (c)

p.1160 LIN/UART Data Field Configuration Register (LDFCn), corrected description of RFDL bits (a)

p.1176 LIN/UART Space Configuration Register (LSCn), added description of IBS bits (c)

p.1181 LIN/UART Status Register (LSTn), deleted description of FTC bit (c)

p.1189 UART Operation Enable Register (LUOERn), added description of UROE bit (c)

p.1216,1217 Table 17-14, Table 17-15 Types of Statuses in LIN Master Mode / LIN Slave Mode, and added Note 1 (c)

p.1218,1221 Table 17-16, Table 17-17 Types of Error Statuses in LIN Master Mode / LIN Slave Mode, corrected Notes 1

and 3

(c)

p.1231 Figure 17-30 Expansion Bit Reception Example (with Data Comparison), added Note (c)

p.1246

to 1249

17.6.2 to 17.6.5 LIN Self-Test Mode, added description when LIN self-test mode is canceled (c)

p.1251,1253

,1255

Figure 17-41, Figure 17-42, Figure 17-43 Block Diagram of Baud Rate Generator, corrected of LIN

communications clock source

(b)

CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

p.1295,1305,

1327,1342,

1372

18.3.7 CiERFLL, 18.3.14 GERFLL, 18.3.35 RFSTSm, 18.3.47 CFSTSk, 18.3.75 THLSTSi, corrected Note (c)

p.1340 18.3.46 CANi Transmit/Receive FIFO Control Register kH (CFCCHk), corrected description of CFITR bit (a)

CHAPTER 19 DTC

p.1461 19.4.3 DTC Pending Instruction, added multiply, divide, and multiply-accumulate instructions (c)

CHAPTER 21 INTERRUPT FUCTIONS

p.1479 Table 21-1 Interrupt Source List (3/4), corrected Note 5 (a)

p.1512 21.4.4 Interrupt servicing during division instruction, added Caution (b)

p.1514 21.4.5 Interrupt request hold, added divide, and multiply-accumulate instructions (c)

CHAPTER 27 SAFETY FUNCTIONS

p.1591 Figure 27-9 Format of 1-bit Error Detection Interrupt Enable Register (ECCIER), added Note 2 (c)

p.1596 27.3.4 CPU stack pointer monitor function, added Caution (b)

p.1601 Figure 27-20 Format of Invalid Memory Access Detection Control Register (IAWCTL), deleted Note 2 (c)

CHAPTER 33 INSTRUCTION SET

p.1672 Table 33-5 Operation List (12/18), added Caution (b)

CHAPTER 34 ELECTRICAL SPECIFICATIONS (GRADE L)

p.1686,1687 34.3.1 Pin Characteristics (1/4) and (2/4), corrected Note 1 (c)

p.1697 34.4.1 Basic Operation (1/2), added RESET pin of Note (c)

p.1708 34.5.1 Serial Array Unit (7) During communication at same potential (simplified I

2

C mode), corrected

Conditions on Table

(a)

p.1729 34.9 Flash Memory Programming Characteristics, corrected Conditions at Erase time (c)

Remark: “Classification” in the above table classifies revisions as follows.

(a): Error correction, (b): Addition/change of specifications, (c): Addition/change of description or note,

(d): Addition/change of package, part number, or management division, (e): Addition/change of related documents

Loading...

Loading...