General-purpose timers (TIM2/TIM3/TIM4/TIM5) RM0351

1000/1830 DocID024597 Rev 5

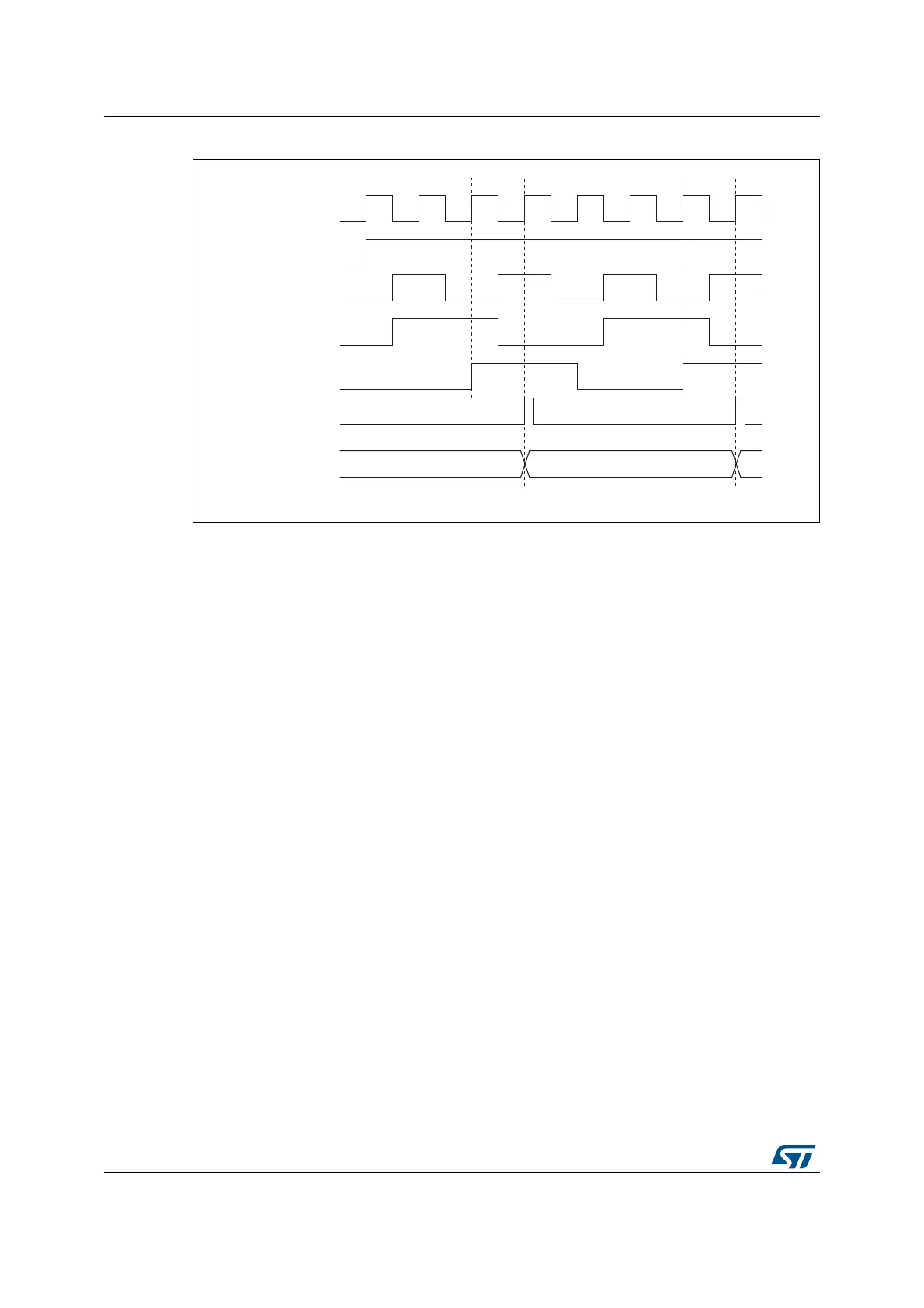

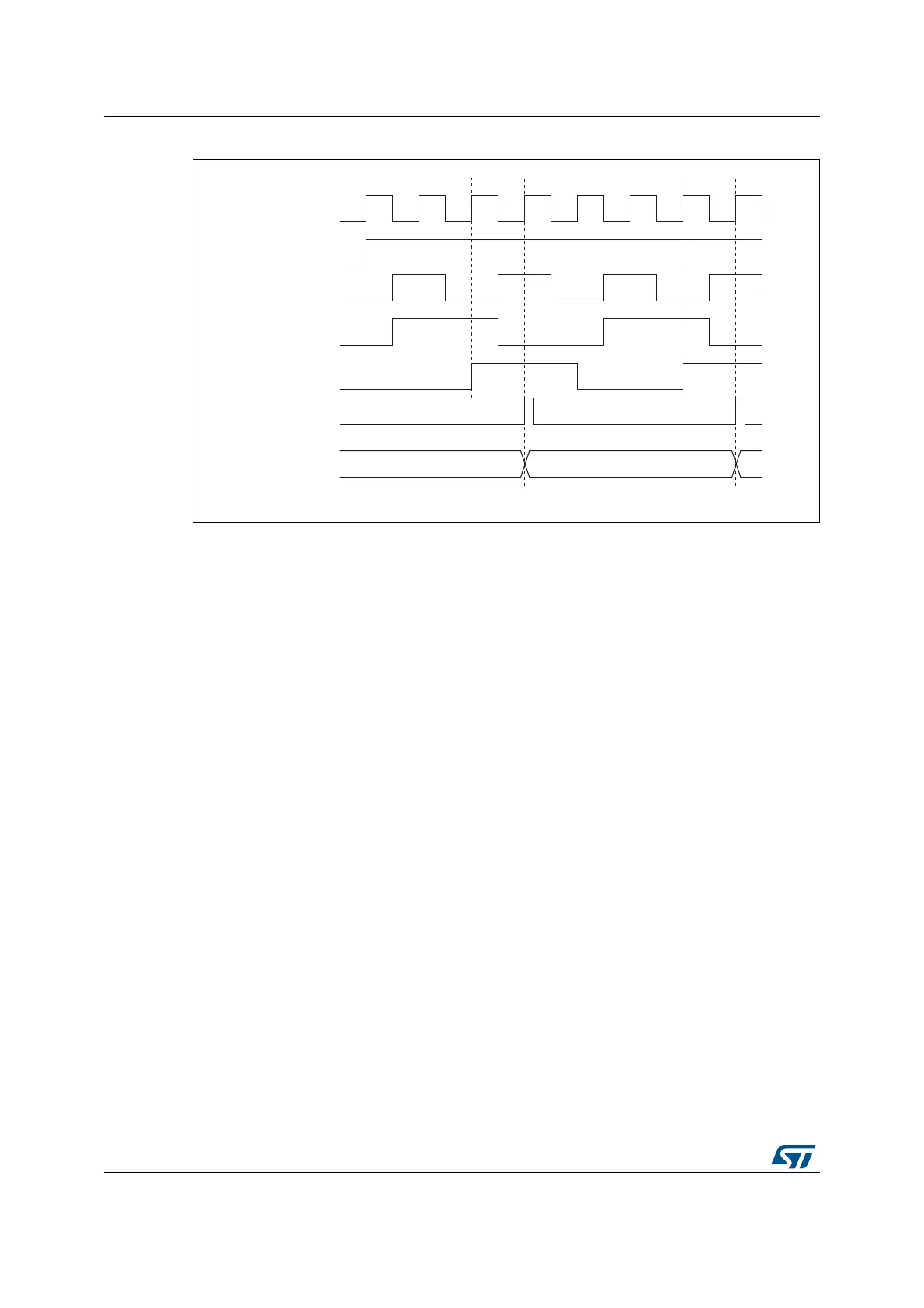

Figure 296. Control circuit in external clock mode 2

31.3.4 Capture/compare channels

Each Capture/Compare channel is built around a capture/compare register (including a

shadow register), a input stage for capture (with digital filter, multiplexing and prescaler) and

an output stage (with comparator and output control).

The following figure gives an overview of one Capture/Compare channel.

The input stage samples the corresponding TIx input to generate a filtered signal TIxF.

Then, an edge detector with polarity selection generates a signal (TIxFPx) which can be

used as trigger input by the slave mode controller or as the capture command. It is

prescaled before the capture register (ICxPS).

069

I

&.B,17

&17B(1

(75

(753

(75)

&RXQWHUFORFN

&.B,17 &.B36&

&RXQWHUUHJLVWHU

Loading...

Loading...