USB on-the-go full-speed (OTG_FS) RM0351

1640/1830 DocID024597 Rev 5

47.11.1 Peripheral FIFO architecture

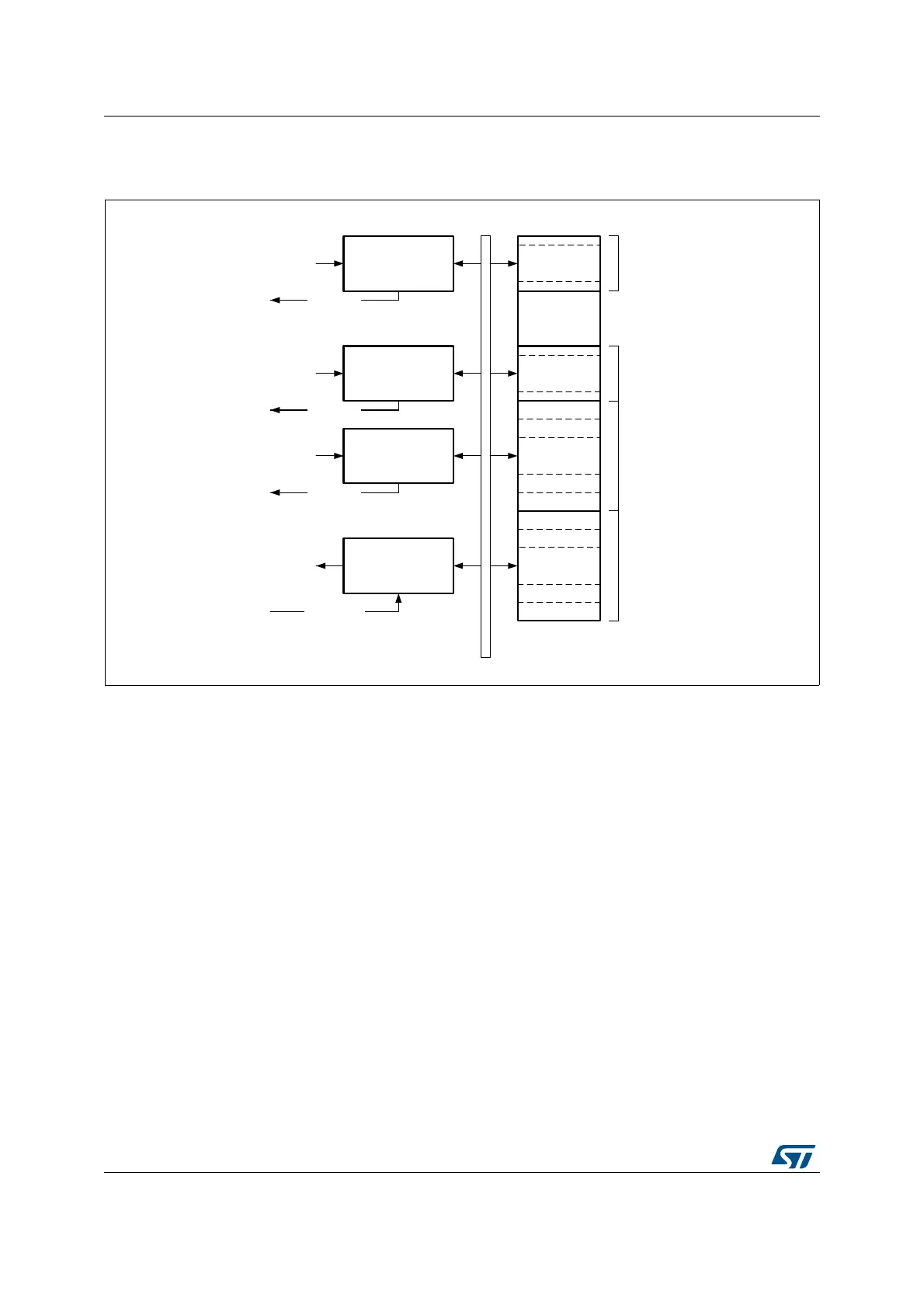

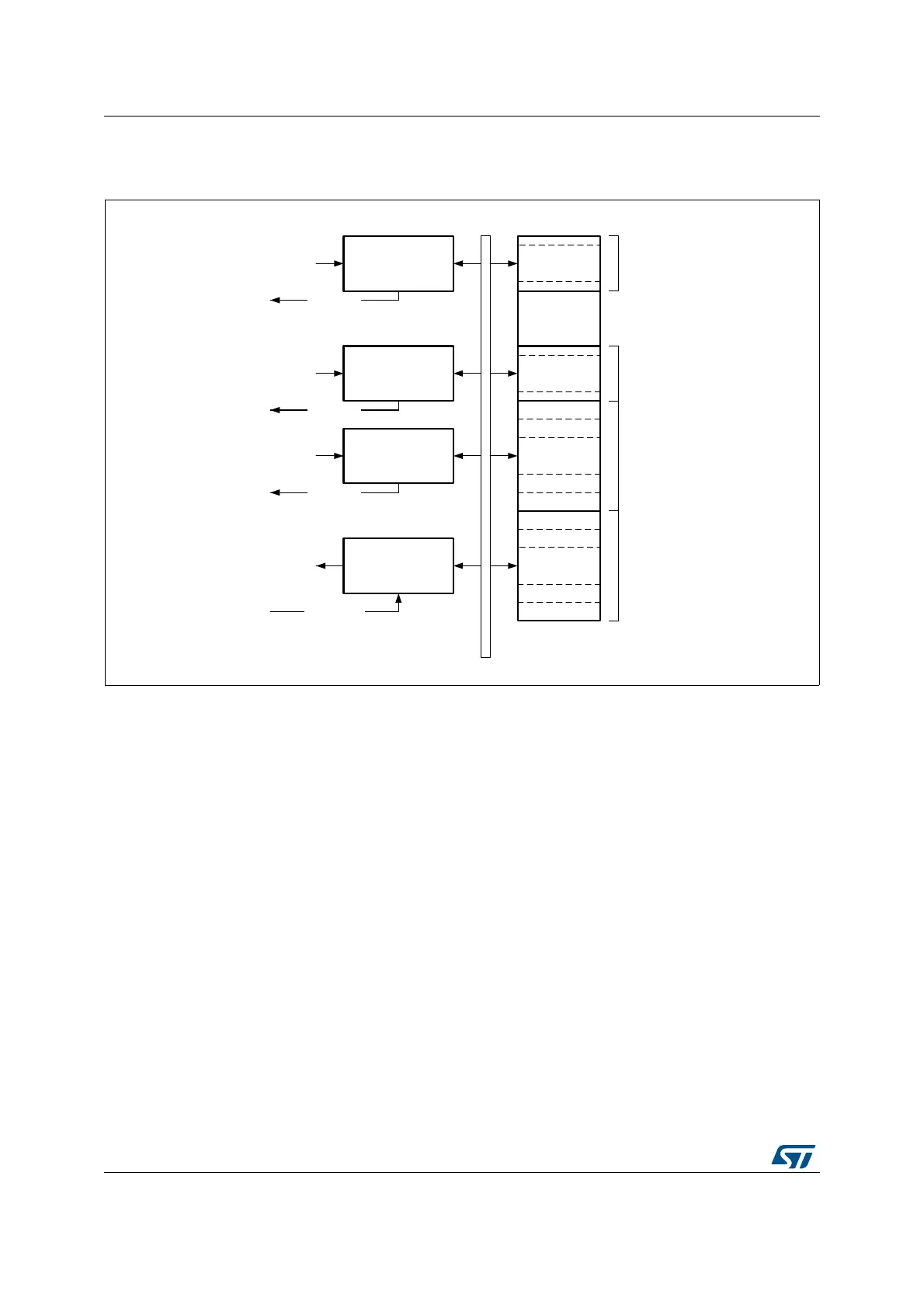

Figure 523. Device-mode FIFO address mapping and AHB FIFO access mapping

Peripheral Rx FIFO

The OTG peripheral uses a single receive FIFO that receives the data directed to all OUT

endpoints. Received packets are stacked back-to-back until free space is available in the Rx

FIFO. The status of the received packet (which contains the OUT endpoint destination

number, the byte count, the data PID and the validity of the received data) is also stored by

the core on top of the data payload. When no more space is available, host transactions are

NACKed and an interrupt is received on the addressed endpoint. The size of the receive

FIFO is configured in the receive FIFO Size register (OTG_GRXFSIZ).

The single receive FIFO architecture makes it more efficient for the USB peripheral to fill in

the receive RAM buffer:

• All OUT endpoints share the same RAM buffer (shared FIFO)

• The OTG_FS core can fill in the receive FIFO up to the limit for any host sequence of

OUT tokens

The application keeps receiving the Rx FIFO non-empty interrupt (RXFLVL bit in

OTG_GINTSTS) as long as there is at least one packet available for download. It reads the

packet information from the receive status read and pop register (OTG_GRXSTSP) and

finally pops data off the receive FIFO by reading from the endpoint-related pop address.

06Y9

'HGLFDWHG7[

),)2[FRQWURO

RSWLRQDO

,1HQGSRLQW7[),)2[

'),)2SXVKDFFHVV

IURP$+%

0$&SRS

7[),)2[

SDFNHW

27*B',(37;)[>@

27*B',(37;)[>@

'HGLFDWHG7[

),)2FRQWURO

RSWLRQDO

,1HQGSRLQW7[),)2

'),)2SXVKDFFHVV

IURP$+%

7[),)2

SDFNHW

27*B',(37;)>@

27*B',(37;)>@

0$&SRS

'HGLFDWHG7[

),)2FRQWURO

RSWLRQDO

,1HQGSRLQW7[),)2

'),)2SXVKDFFHVV

IURP$+%

7[),)2

SDFNHW

27*B',(37;)>@

27*B',(37;)>@

0$&SRS

'HGLFDWHG7[

),)2FRQWURO

RSWLRQDO

$Q\287HQGSRLQW

'),)2SRSDFFHVV

IURP$+%

5[SDFNHWV

27*B*5;)6,=>@

0$&SXVK

$ 5[VWDUWDGGUHVVIL[HG

WR

6LQJOHGDWD

),)2

Loading...

Loading...