Single Wire Protocol Master Interface (SWPMI) RM0351

1506/1830 DocID024597 Rev 5

Any further write to the SWPMI_TDR register while TXUNRF is set will be ignored. The user

must set CTXUNRF bit in the SWPMI_ICR register to clear TXUNRF flag.

Overrun during payload reception

During the reception of the frame payload, a receive overrun is indicated by RXOVRF flag in

the SWPMI_ISR register. If a receive overrun occurs, the SWPMI does not update

SWPMI_RDR with the incoming data. The incoming data will be lost.

The reception carries on up to the EOF and, if the overrun condition disappears, the RXBFF

flag is set. When RXBFF flag is set, the user can check the RXOVRF flag. The user must

set CRXOVRF bit in the SWPMI_ICR register to clear RXBOVRF flag.

If the user wants to detect the overrun immediately, RXBOVREIE bit in the SWPMI_IER

register can be set in order to generate an interrupt as soon as the overrun occurs.

The RXOVRF flag is set at the same time as the RXNE flag, two SWPMI_RDR reads after

the overrun event occurred. It indicates that at least one received byte was lost, and the

loaded word in SWPMI_RDR contains the bytes received just before the overrun.

In Multi software buffer mode, if RXOVRF flag is set for the last word of the received frame,

then the overrun bit (bit 25 of the 8th word) is set for both the current and the next frame.

CRC error during payload reception

Once the two CRC bytes have been received, if the CRC is wrong, the RXBERF flag in the

SWPMI_ISR register is set after the EOF reception. An interrupt is generated if RXBEIE bit

in the SWPMI_IER register is set (refer toFigure 486: SWPMI single buffer mode reception

with CRC error).The user must set CRXBERF bit in SWPMI_ICR to clear RXBERF flag.

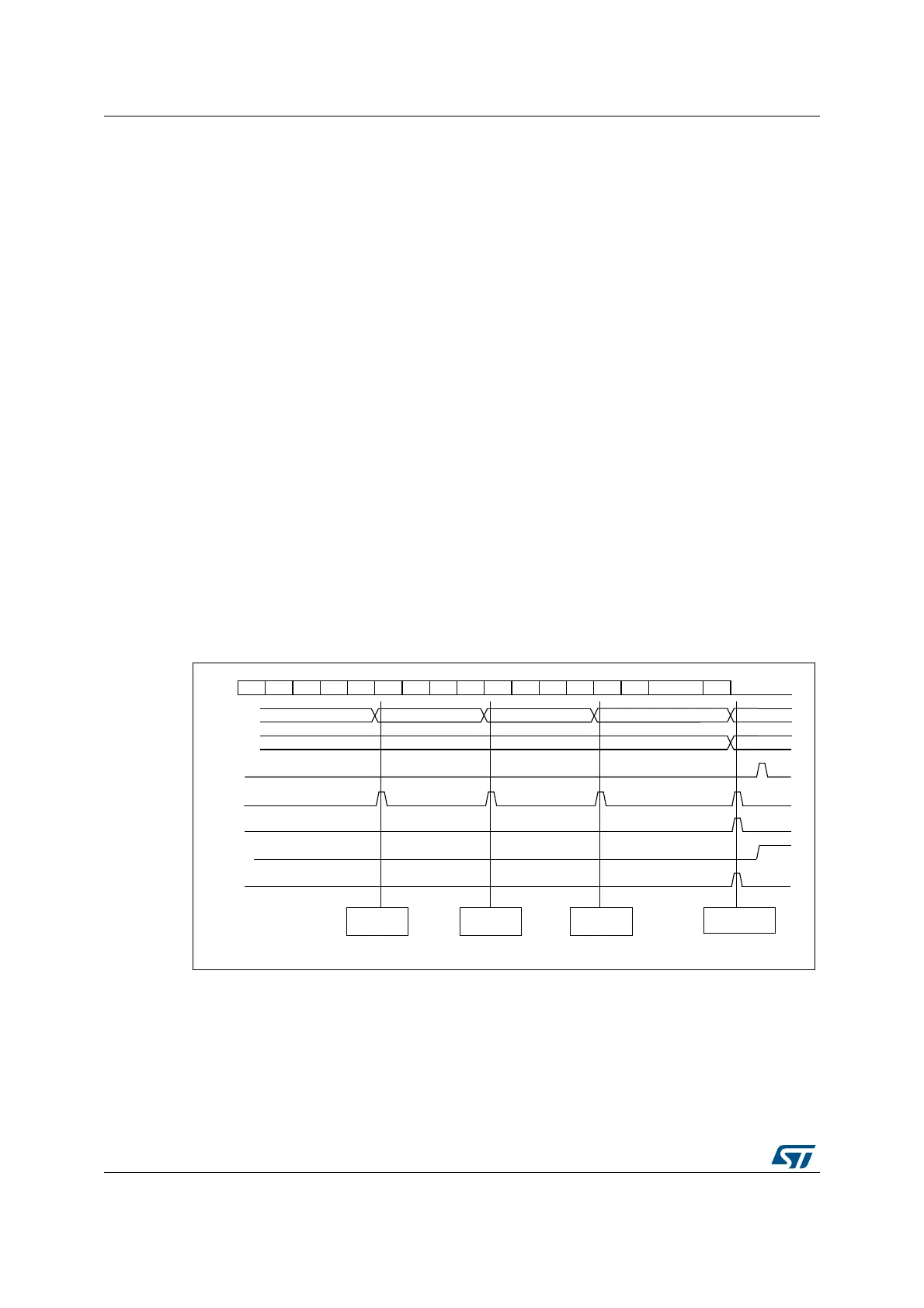

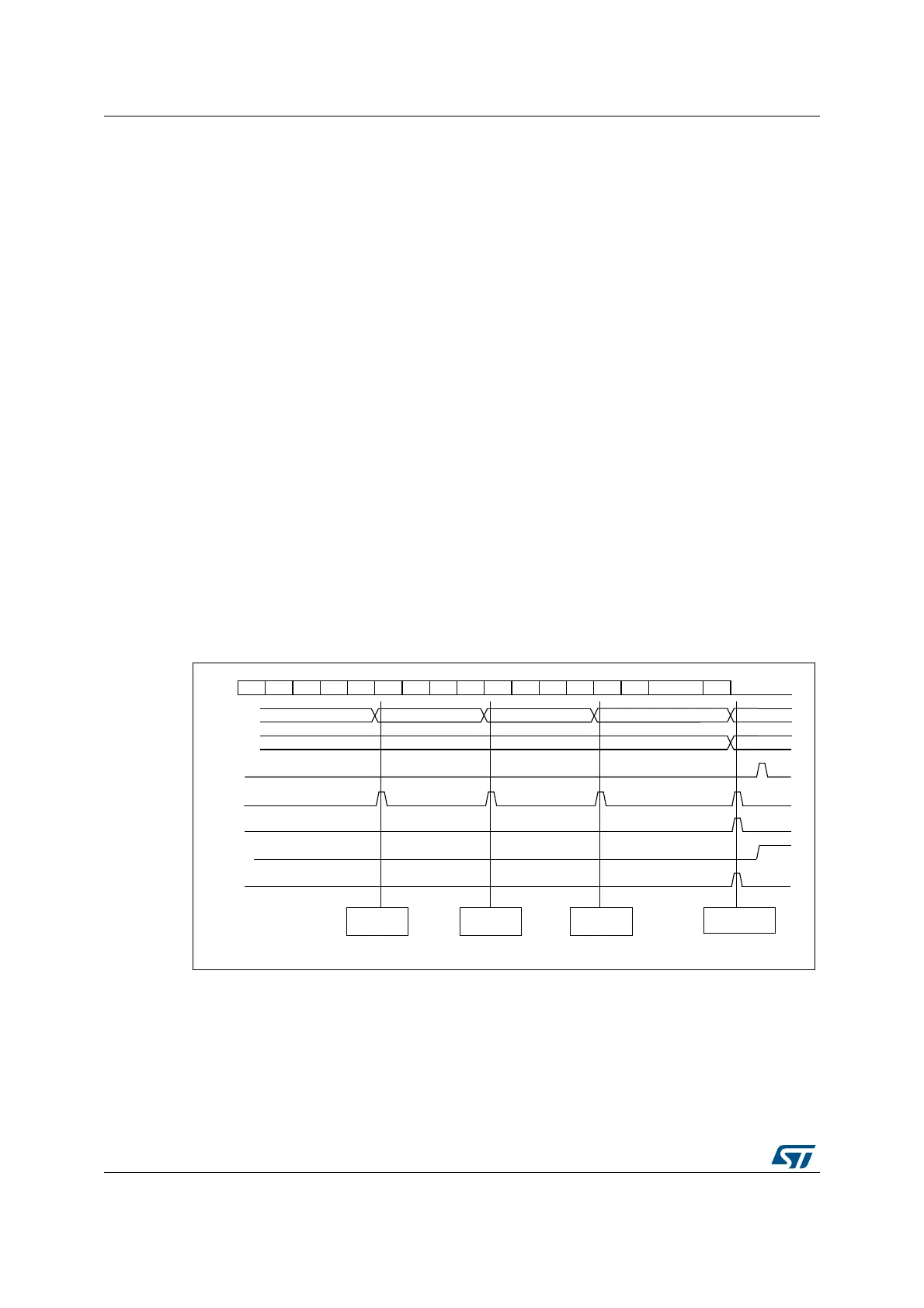

Figure 486. SWPMI single buffer mode reception with CRC error

Missing or corrupted stuffing bit during payload reception

When a stuffing bit is missing or is corrupted in the payload, RXBERF and RXBFF flags are

set in SWPMI_ISR after the EOF reception.

069

^K& K&ZϬ ϭ Ϯ ϯ ϰ ϱ ϲ ϳ ϴ ϵ ϭϬ ϭϭ ϭϮ

^tW

ŝŶƉƵƚ

ZyE

^tWD/ͺZZ

Zy&&

ϯͲϮͲϭͲϬ ϳͲϲͲϱͲϰ ϭϭͲϭϬͲϵͲϴ džͲdžͲϭϯͲϭϮ

džͲdžͲdžͲdž

dž ϭϰĚ

^tWD/ͺZ&>

ϭϯ

^h^WE

^tƌĞĂĚƐ

^tWD/ͺZZ

d&

^tĚĞƚĞĐƚƐĞƌƌŽƌ

ǁŝƚŚZyZ&ĨůĂŐ

ZyZ&

^tƌĞĂĚƐ

^tWD/ͺZZ

^tƌĞĂĚƐ

^tWD/ͺZZ

VHWE\+:FOHDUHGE\6:

VHWE\+:

VHWE\+:FOHDUHGE\6:

VHWE\+:FOHDUHGE\6:RU'0$

VHWE\+:FOHDUHGE\6:

Loading...

Loading...