General-purpose timers (TIM2/TIM3/TIM4/TIM5) RM0351

994/1830 DocID024597 Rev 5

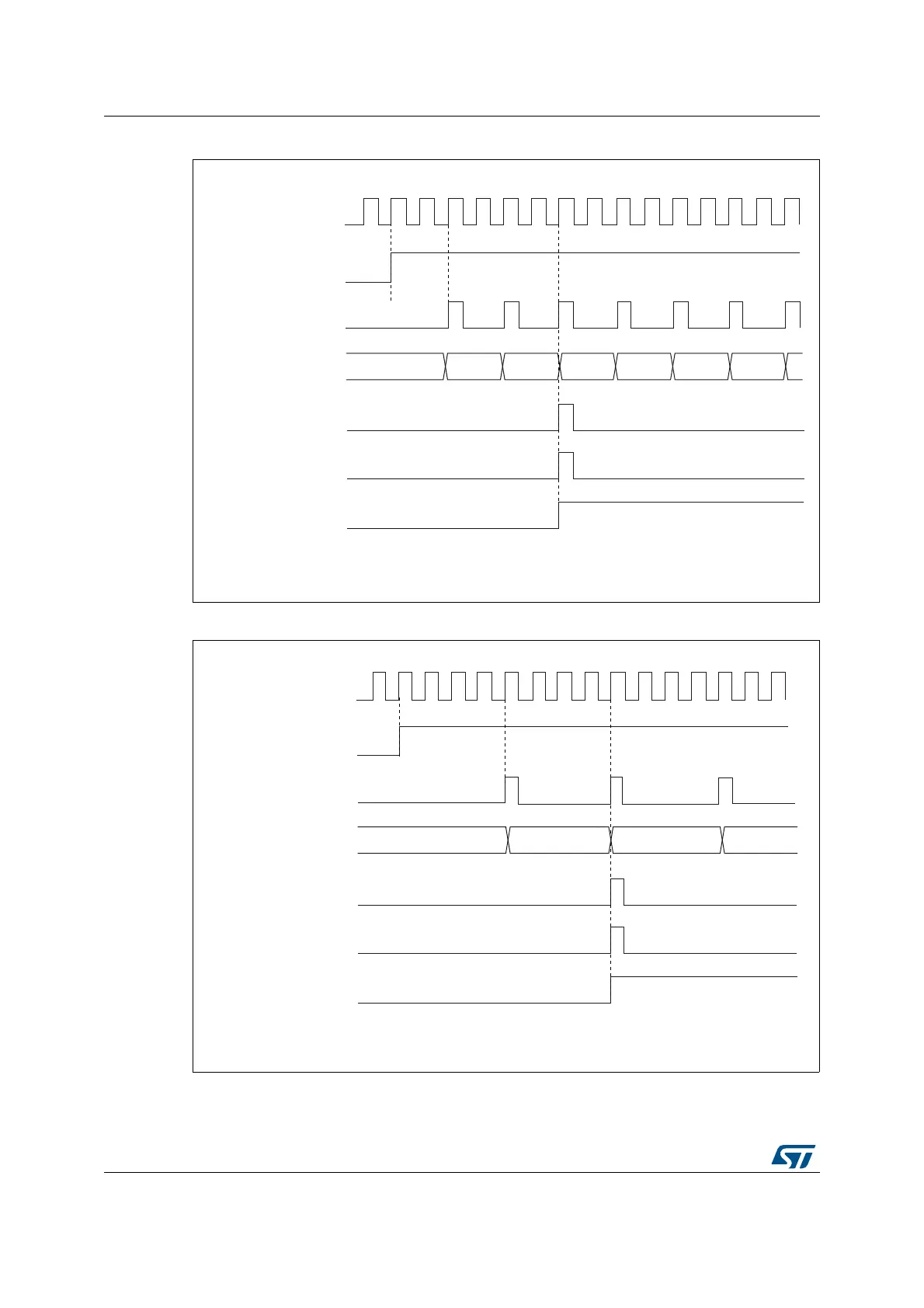

Figure 287. Counter timing diagram, internal clock divided by 2

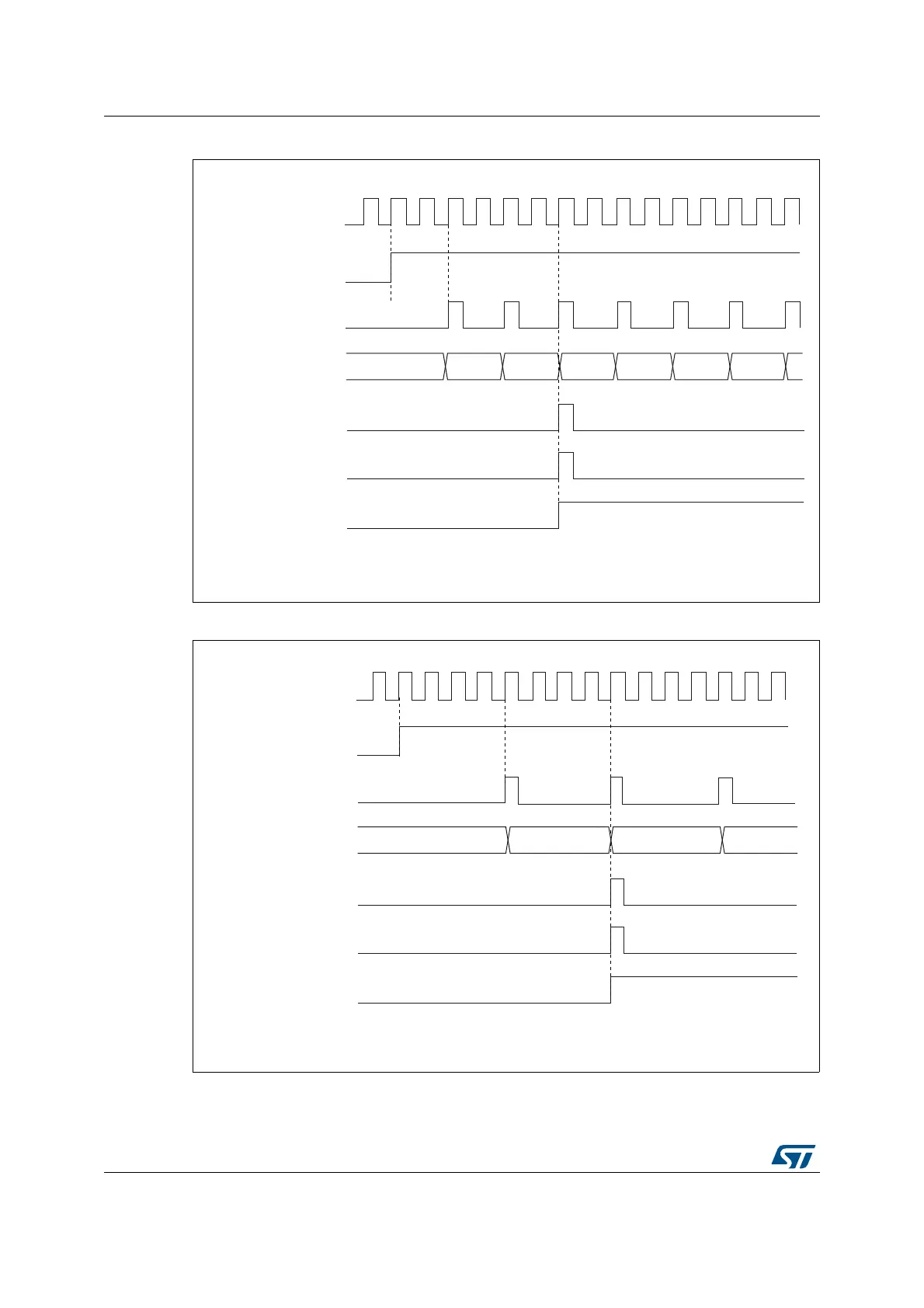

Figure 288. Counter timing diagram, internal clock divided by 4, TIMx_ARR=0x36

1. Center-aligned mode 2 or 3 is used with an UIF on overflow.

069

&.B36&

&17B(1

7LPHUFORFN &.B&17

&RXQWHUUHJLVWHU

8SGDWHHYHQW8(9

&RXQWHUXQGHUIORZ

8SGDWHLQWHUUXSWIODJ

8,)

069

&.B36&

7LPHUFORFN &.B&17

&RXQWHUUHJLVWHU

8SGDWHHYHQW8(9

&RXQWHURYHUIORZ

8SGDWHLQWHUUXSWIODJ

8,)

&17B(1

1RWH+HUHFHQWHUBDOLJQHGPRGHRULVXSGDWHGZLWKDQ8,)RQRYHUIORZ

Loading...

Loading...