Extended interrupts and events controller (EXTI) RM0351

398/1830 DocID024597 Rev 5

To generate an event, the event line should be configured and enabled. This is done by

programming the two trigger registers with the desired edge detection and by enabling the

event request by writing a ‘1’ to the corresponding bit in the event mask register. When the

selected edge occurs on the event line, an event pulse is generated. The pending bit

corresponding to the event line is not set.

For the configurable lines, an interrupt/event request can also be generated by software by

writing a ‘1’ in the software interrupt/event register.

Note: The interrupts or events associated to the direct lines are triggered only when the system is

in Stop mode. If the system is still running, no interrupt/event is generated by the EXTI.

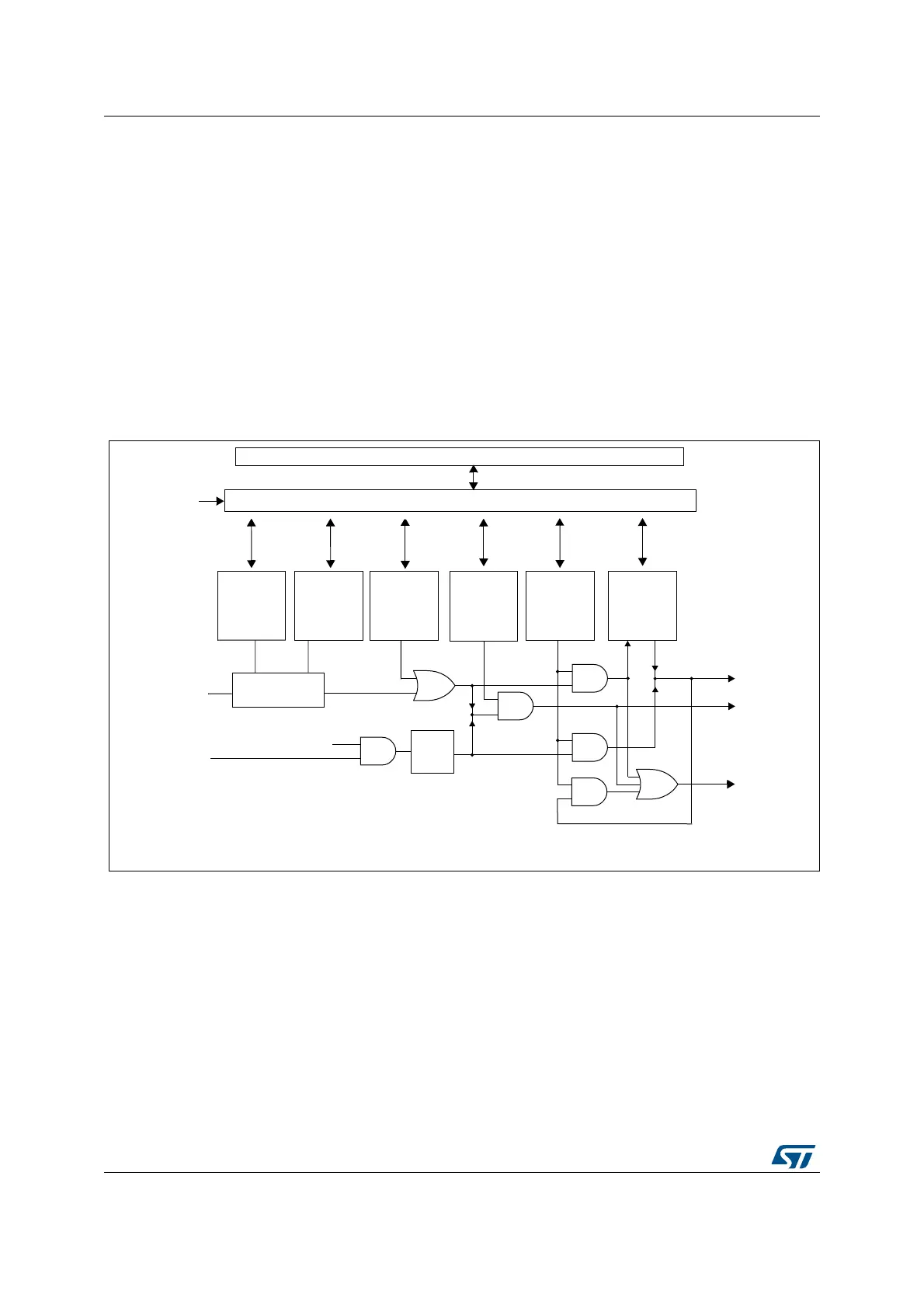

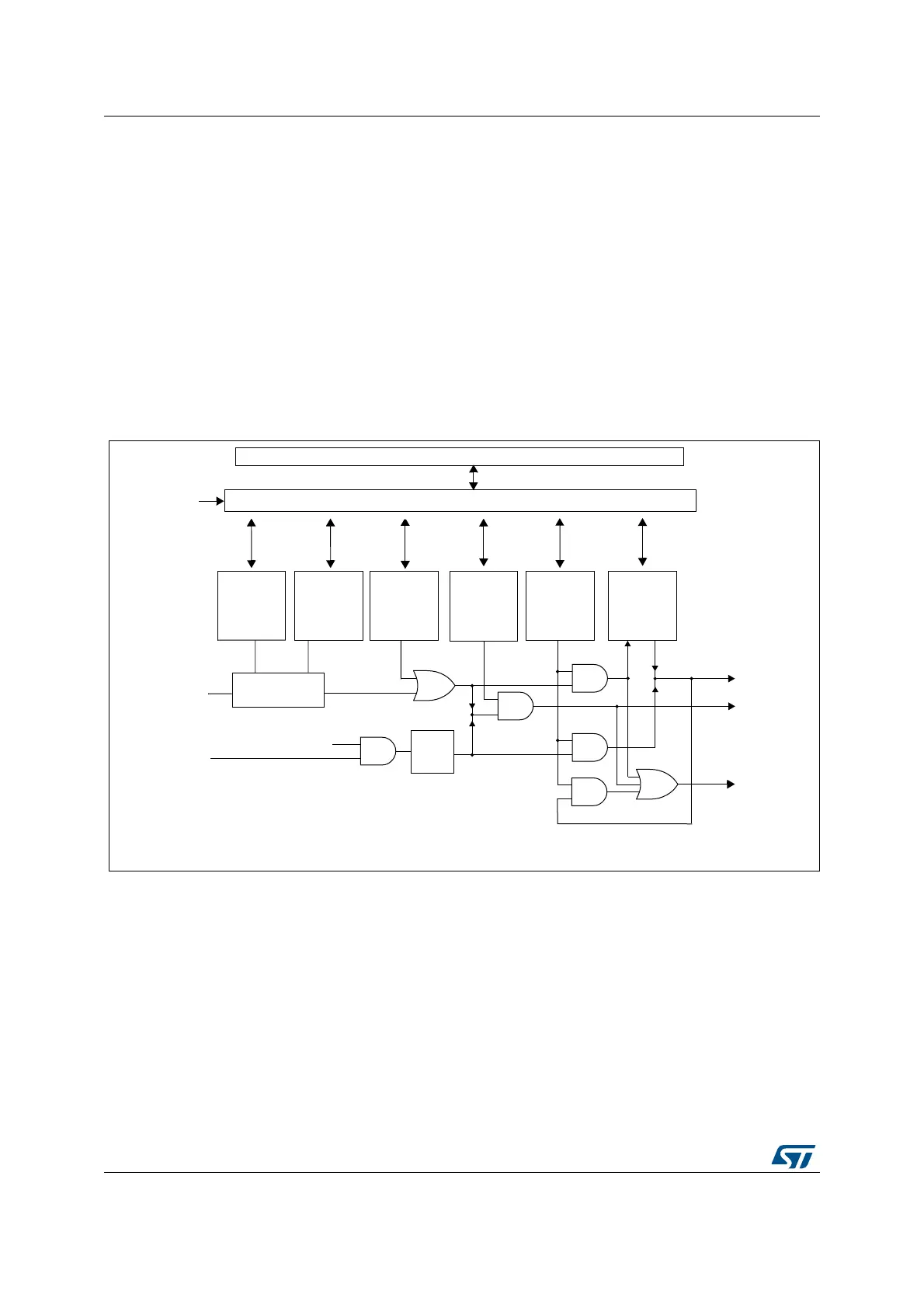

14.3.1 EXTI block diagram

The extended interrupt/event block diagram is shown on Figure 33.

Figure 33. Configurable interrupt/event block diagram

14.3.2 Wakeup event management

The STM32L4x5/STM32L4x6 is able to handle external or internal events in order to wake

up the core (WFE). The wakeup event can be generated either by:

• enabling an interrupt in the peripheral control register but not in the NVIC, and enabling

the SEVONPEND bit in the Cortex

TM

-M4 System Control register. When the MCU

resumes from WFE, the EXTI peripheral interrupt pending bit and the peripheral NVIC

IRQ channel pending bit (in the NVIC interrupt clear pending register) have to be

cleared

• or by configuring an EXTI line in event mode. When the CPU resumes from WFE, it is

not necessary to clear the peripheral interrupt pending bit or the NVIC IRQ channel

pending bit as the pending bit corresponding to the event line is not set.

3HULSKHUDOLQWHUIDFH

(GJHGHWHFW

FLUFXLW

$3%EXV

3&/.

,QWHUUXSWV

6RIWZDUH

LQWHUUXSW

HYHQW

UHJLVWHU

5LVLQJ

WULJJHU

VHOHFWLRQ

UHJLVWHU

3HQGLQJ

UHTXHVW

UHJLVWHU

069

,QWHUUXSW

PDVN

UHJLVWHU

)DOOLQJ

WULJJHU

VHOHFWLRQ

UHJLVWHU

(YHQW

PDVN

UHJLVWHU

3JTJOH

FEHF

EFUFDU

6WRSPRGH

'LUHFWHYHQWV

&RQILJXUDEOH

HYHQWV

(YHQWV

:DNHXS

Loading...

Loading...