System and memory overview RM0351

70/1830 DocID024597 Rev 5

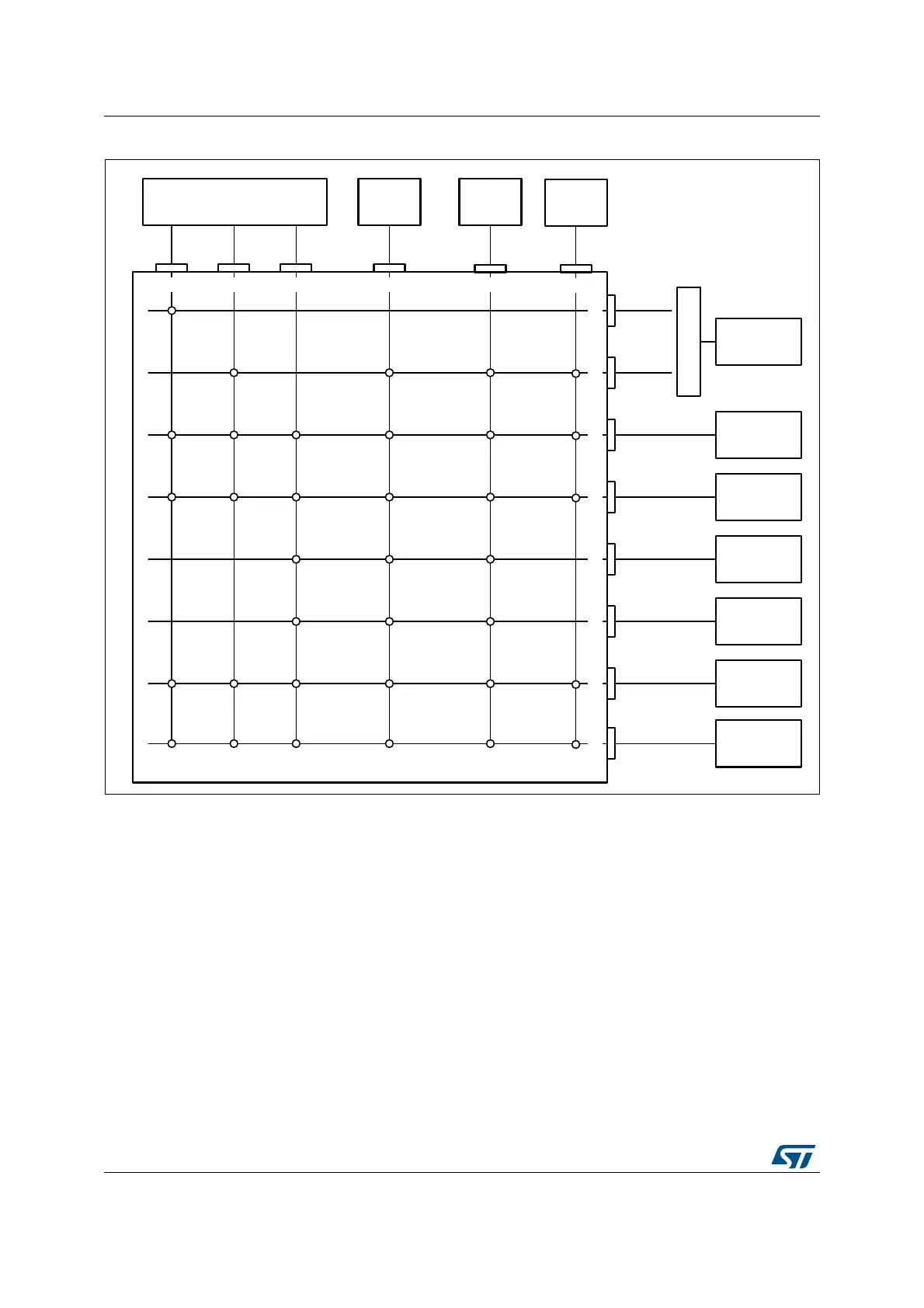

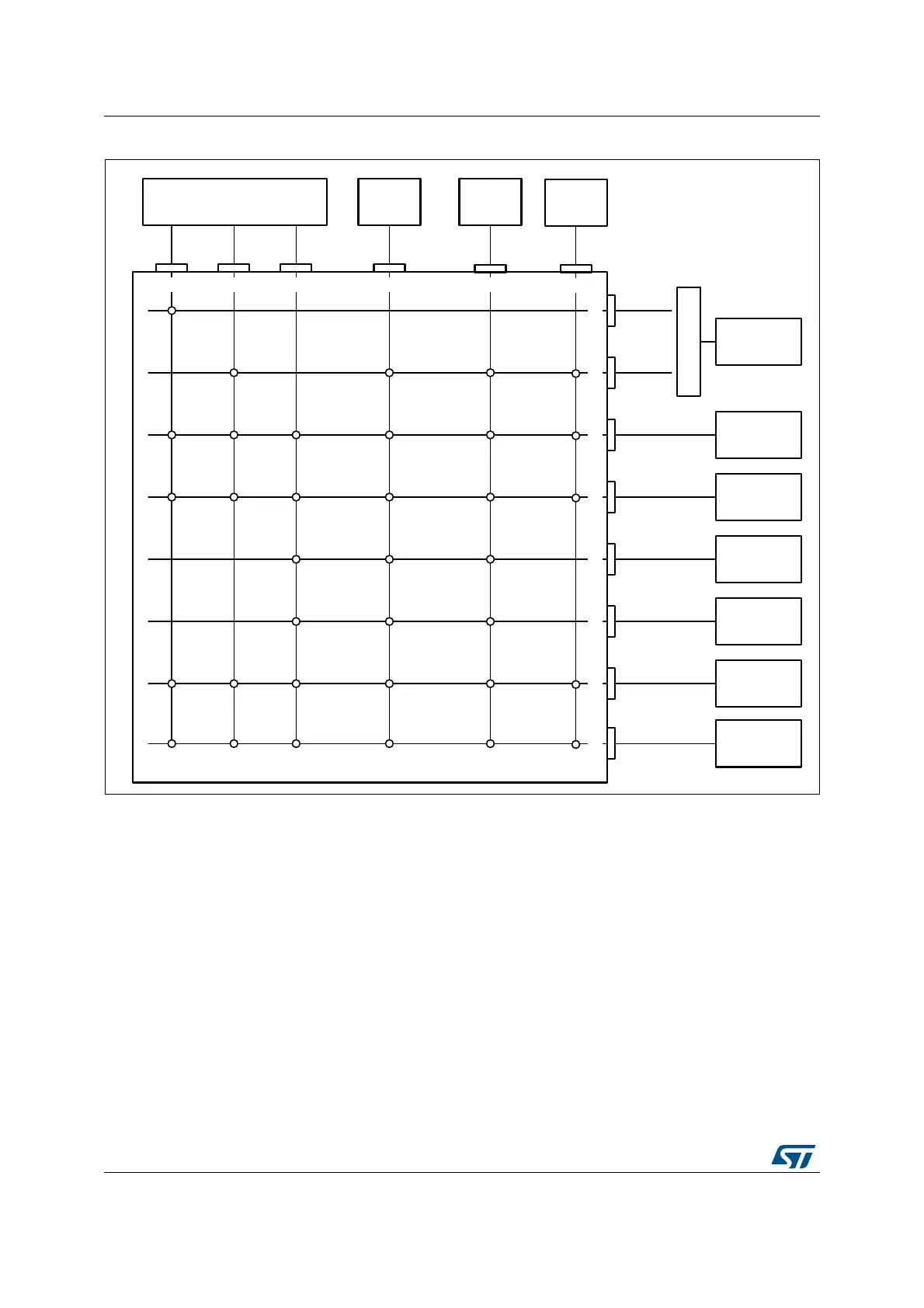

Figure 2. System architecture for STM32L496xx/4A6xx devices

2.1.1 S0: I-bus

This bus connects the instruction bus of the Cortex

®

-M4 core to the BusMatrix. This bus is

used by the core to fetch instructions. The targets of this bus are the internal Flash memory,

SRAM1, SRAM2 and external memories through QUADSPI or the FMC.

2.1.2 S1: D-bus

This bus connects the data bus of the Cortex

®

-M4 core to the BusMatrix. This bus is used

by the core for literal load and debug access. The targets of this bus are the internal Flash

memory, SRAM1, SRAM2 and external memories through QUADSPI or the FMC.

2.1.3 S2: S-bus

This bus connects the system bus of the Cortex

®

-M4 core to the BusMatrix. This bus is

used by the core to access data located in a peripheral or SRAM area. The targets of this

06Y9

$50

&257(;

0ZLWK)38

'0$ '0$

)0&

$+%

SHULSKHUDOV

$+%

SHULSKHUDOV

65$0

65$0

)/$6+

0%

$&&(/

6 6 6 6 6

0 0 0 0 0 0 0

,&RGH

'&RGH

48$'63,

0

'0$'

6

%XV0DWUL[6

Loading...

Loading...