DocID024597 Rev 5 1657/1830

RM0351 USB on-the-go full-speed (OTG_FS)

1774

47.15.5 OTG reset register (OTG_GRSTCTL)

Address offset: 0x10

Reset value: 0x8000 0000

The application uses this register to reset various hardware features inside the core.

Bit 6 PHYSEL: Full Speed serial transceiver select

This bit is always 1 with read-only access.

Bits 5:3 Reserved, must be kept at reset value.

Bits 2:0 TOCAL: FS timeout calibration

The number of PHY clocks that the application programs in this field is added to the full-

speed interpacket timeout duration in the core to account for any additional delays

introduced by the PHY. This can be required, because the delay introduced by the PHY in

generating the line state condition can vary from one PHY to another.

The USB standard timeout value for full-speed operation is 16 to 18 (inclusive) bit times. The

application must program this field based on the speed of enumeration. The number of bit

times added per PHY clock is 0.25 bit times.

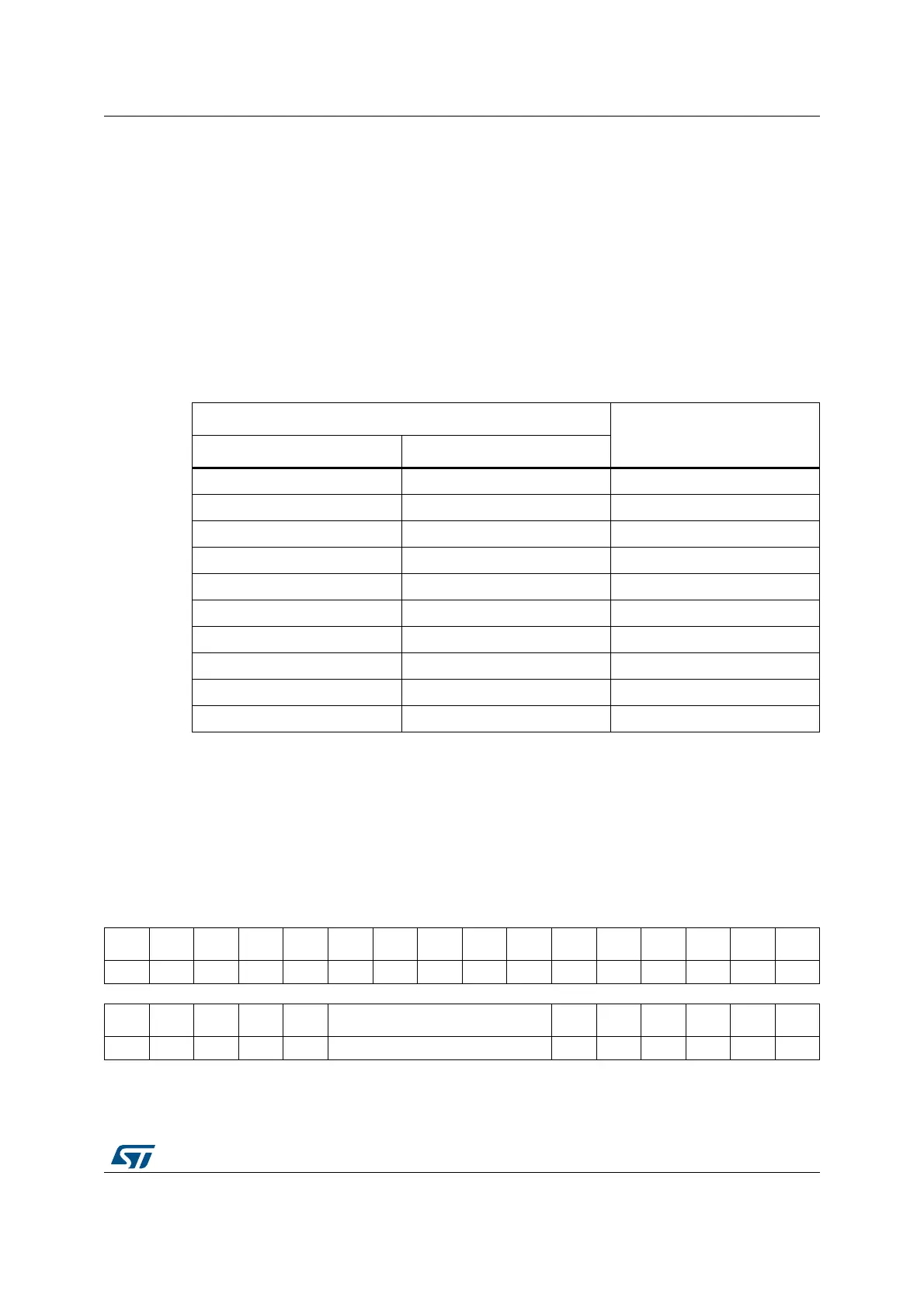

Table 307. TRDT values(FS)

AHB frequency range (MHz)

TRDT minimum value

Min Max

14.2 15 0xF

15 16 0xE

16 17.2 0xD

17.2 18.5 0xC

18.5 20 0xB

20 21.8 0xA

21.8 24 0x9

24 27.5 0x8

27.5 32 0x7

32 - 0x6

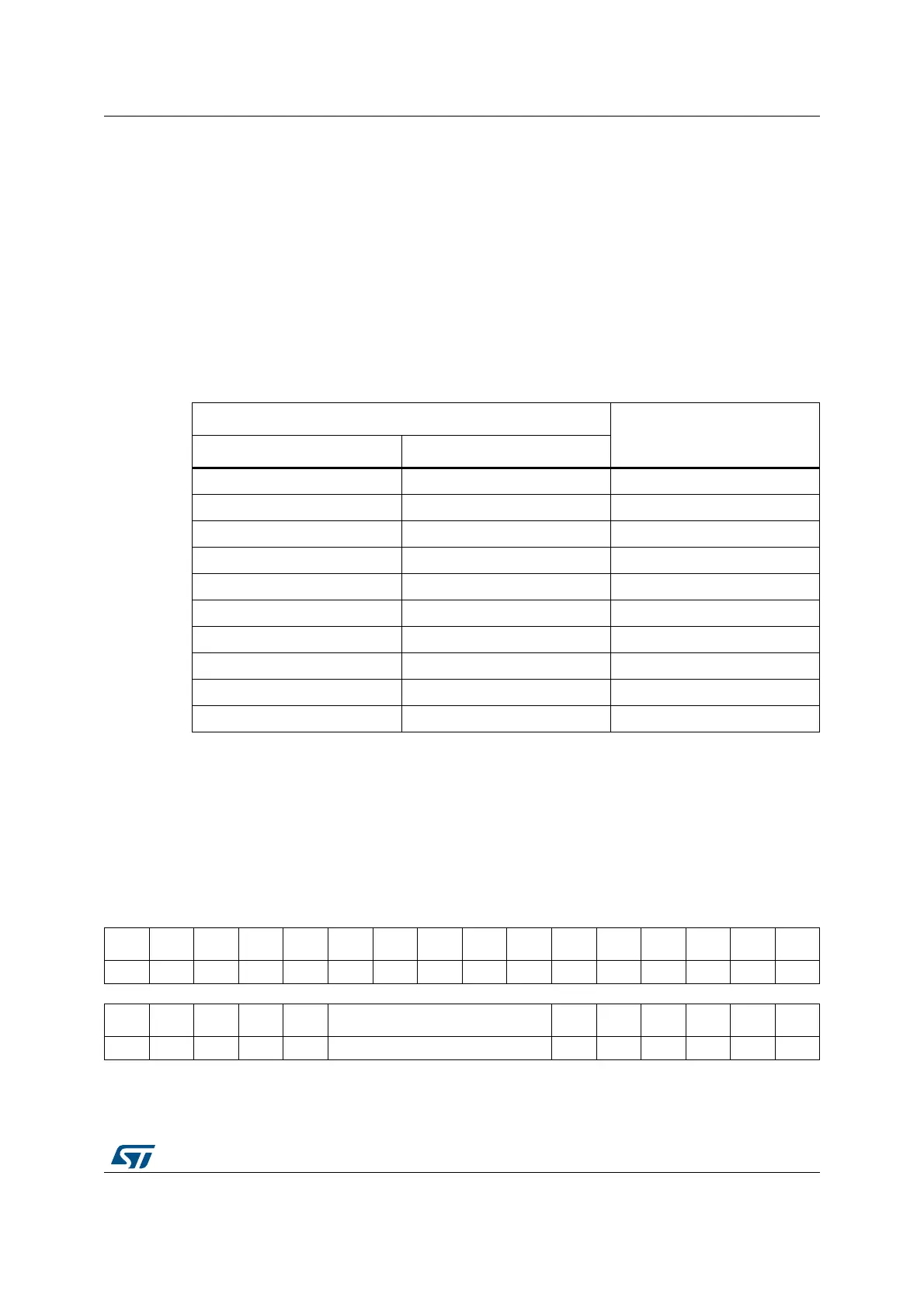

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

AHB

IDL

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

r r

1514131211109876543210

Res. Res. Res. Res. Res. TXFNUM

TXF

FLSH

RXF

FLSH

Res. FCRST PSRST CSRST

rw rs rs rs rs

r

Loading...

Loading...