Digital filter for sigma delta modulators (DFSDM) RM0351

710/1830 DocID024597 Rev 5

Clock absence detection

Channels serial clock inputs can be checked for clock absence/presence to ensure the

correct operation of conversion and error reporting. Clock absence detection can be

enabled or disabled on each input channel y by bit CKABEN in DFSDM_CHyCFGR1

register. If enabled, then this clock absence detection is performed continuously on a given

channel. A clock absence flag is set (CKABF[y] = 1) and an interrupt can be invoked (if

CKABIE=1) in case of an input clock error (see CKABF[7:0] in DFSDM_FLT0ISR register

and CKABEN in DFSDM_CHyCFGR1). After a clock absence flag clearing (by CLRCKABF

in DFSDM_FLT0ICR register), the clock absence flag is refreshed. Clock absence status bit

CKABF[y] is set also by hardware when corresponding channel y is disabled (if CHEN[y] = 0

then CKABF[y] is held in set state).

When a clock absence event has occurred, the data conversion (and/or analog watchdog

and short-circuit detector) provides incorrect data. The user should manage this event and

discard given data while a clock absence is reported.

The clock absence feature is available only when the system clock is used for the CKOUT

signal (CKOUTSRC=0 in DFSDM_CH0CFGR1 register).

When the transceiver is not yet synchronized, the clock absence flag is set and cannot be

cleared by CLRCKABF[y] bit (in DFSDM_FLT0ICR register). The software sequence

concerning clock absence detection feature should be:

• Enable given channel by CHEN = 1

• Try to clear the clock absence flag (by CLRCKABF = 1) until the clock absence flag is

really cleared (CKABF = 0). At this time, the transceiver is synchronized (signal clock is

valid) and is able to receive data.

• Enable the clock absence feature CKABEN = 1 and the associated interrupt CKABIE =

1 to detect if the SPI clock is lost or Manchester data edges are missing.

If SPI data format is used, then the clock absence detection is based on the comparison of

an external input clock with an output clock generation (CKOUT signal). The external input

clock signal into the input channel must be changed at least once per 8 signal periods of

CKOUT signal (which is controlled by CKOUTDIV field in DFSDM_CH0CFGR1 register).

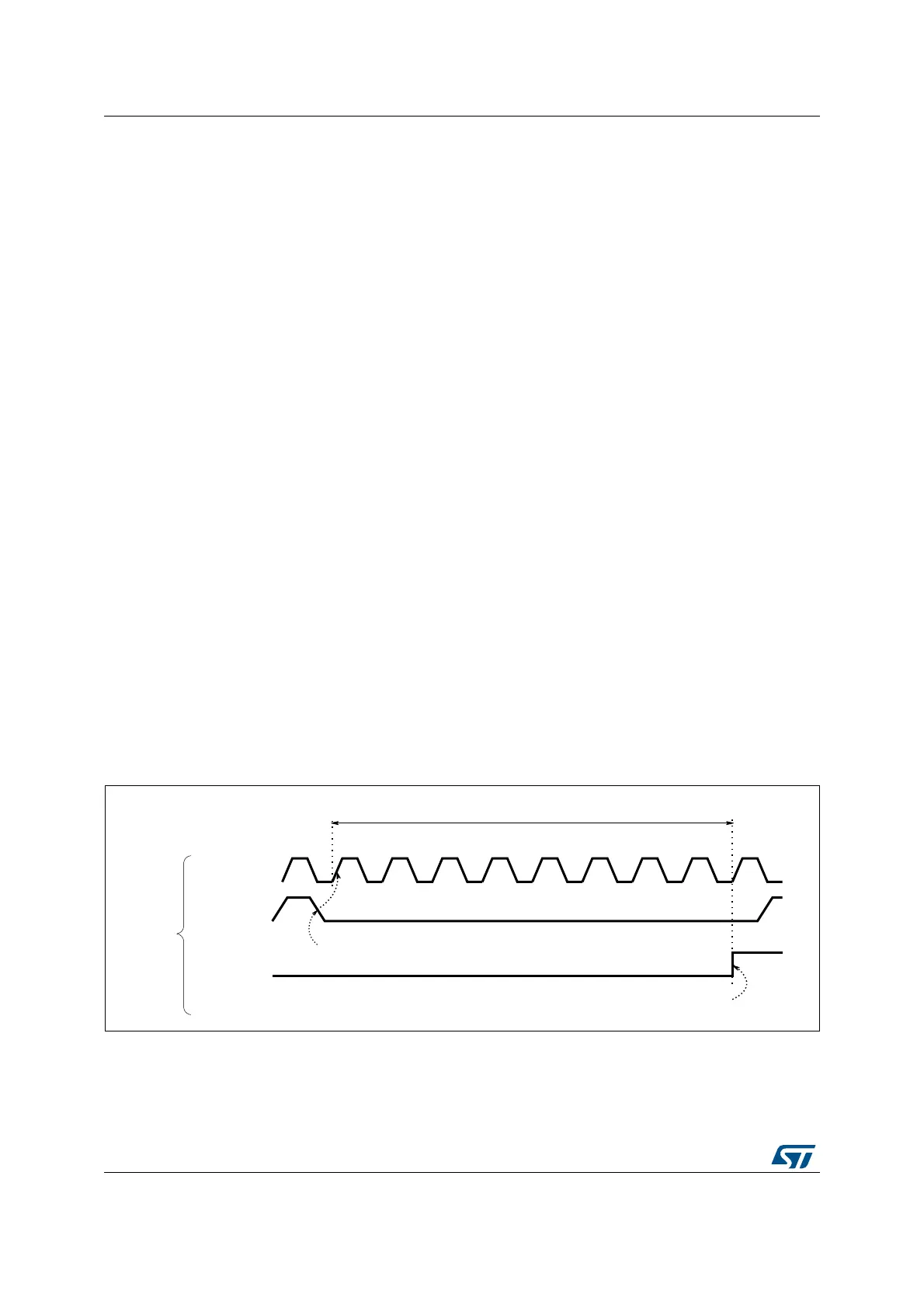

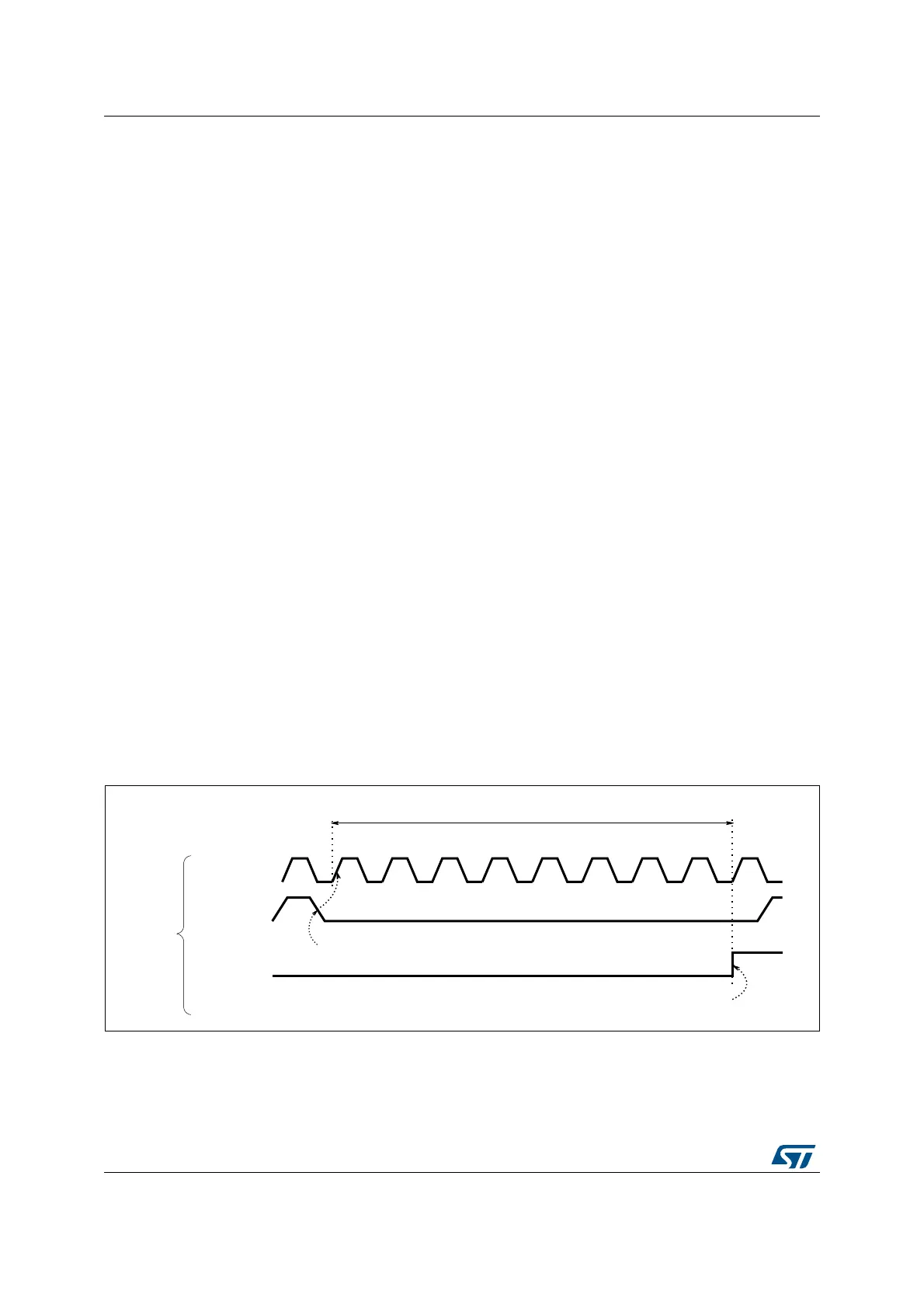

Figure 166. Clock absence timing diagram for SPI

If Manchester data format is used, then the clock absence means that the clock recovery is

unable to perform from Manchester coded signal. For a correct clock recovery, it is first

necessary to receive data with 1 to 0 or 0 to 1 transition (see Figure 168 for Manchester

synchronization).

069

&.287

63,FORFNSUHVHQFH

WLPLQJ

PD[SHULRGV

&.,1\

ODVWFORFNFKDQJH

&.$%)>\@

HUURUUHSRUWHG

UHVWDUWFRXQWLQJ

Loading...

Loading...