Hash processor (HASH) RM0351

864/1830 DocID024597 Rev 5

The above interrupt sources can be enabled or disabled individually by changing the mask

bits in the HASH_IMR register. Setting the appropriate mask bit to 1 enables the interrupt.

The status of the individual interrupt events can be read from the HASH_SR register.

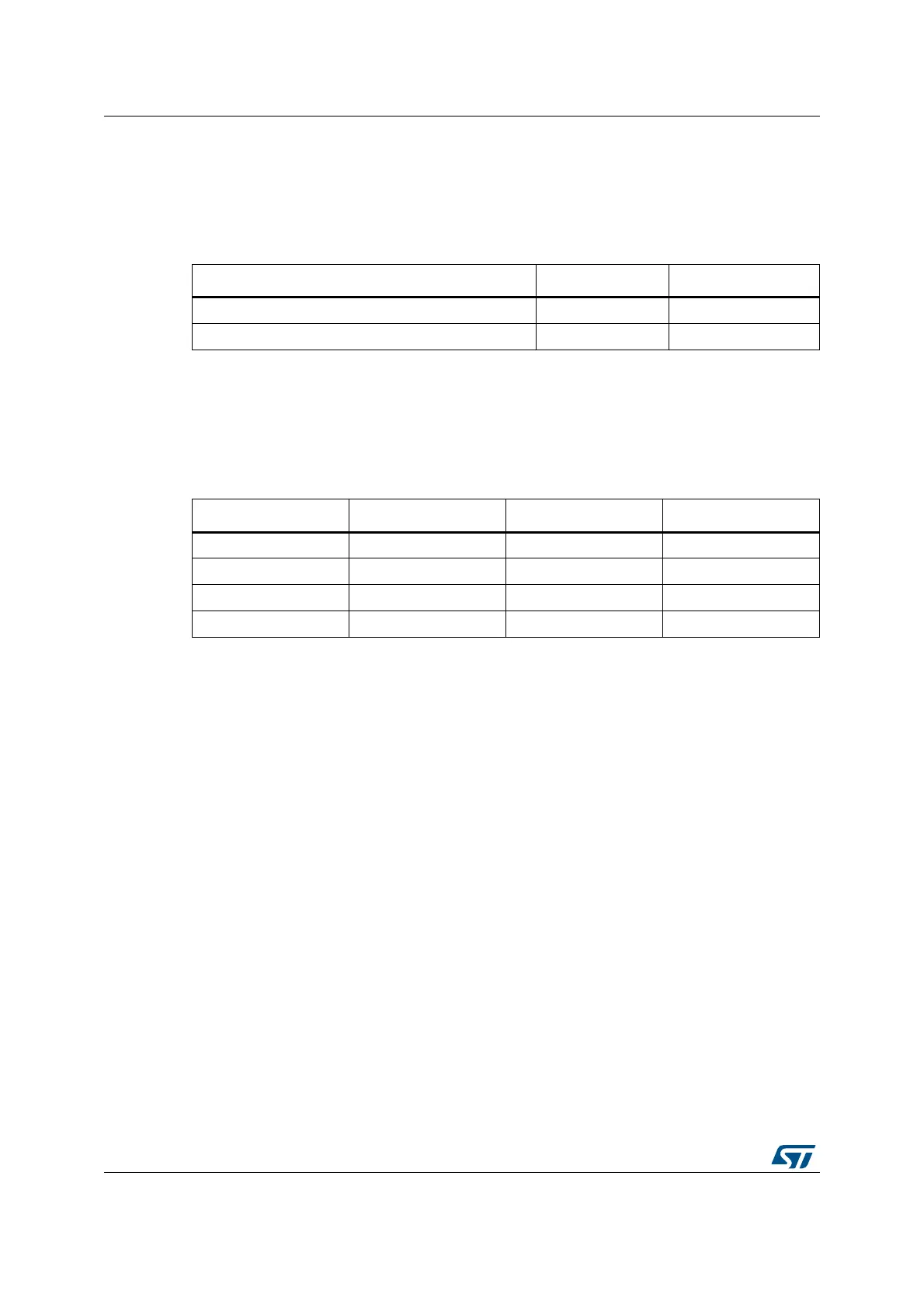

Table 182 gives a summary of the available features.

29.5 HASH processing time

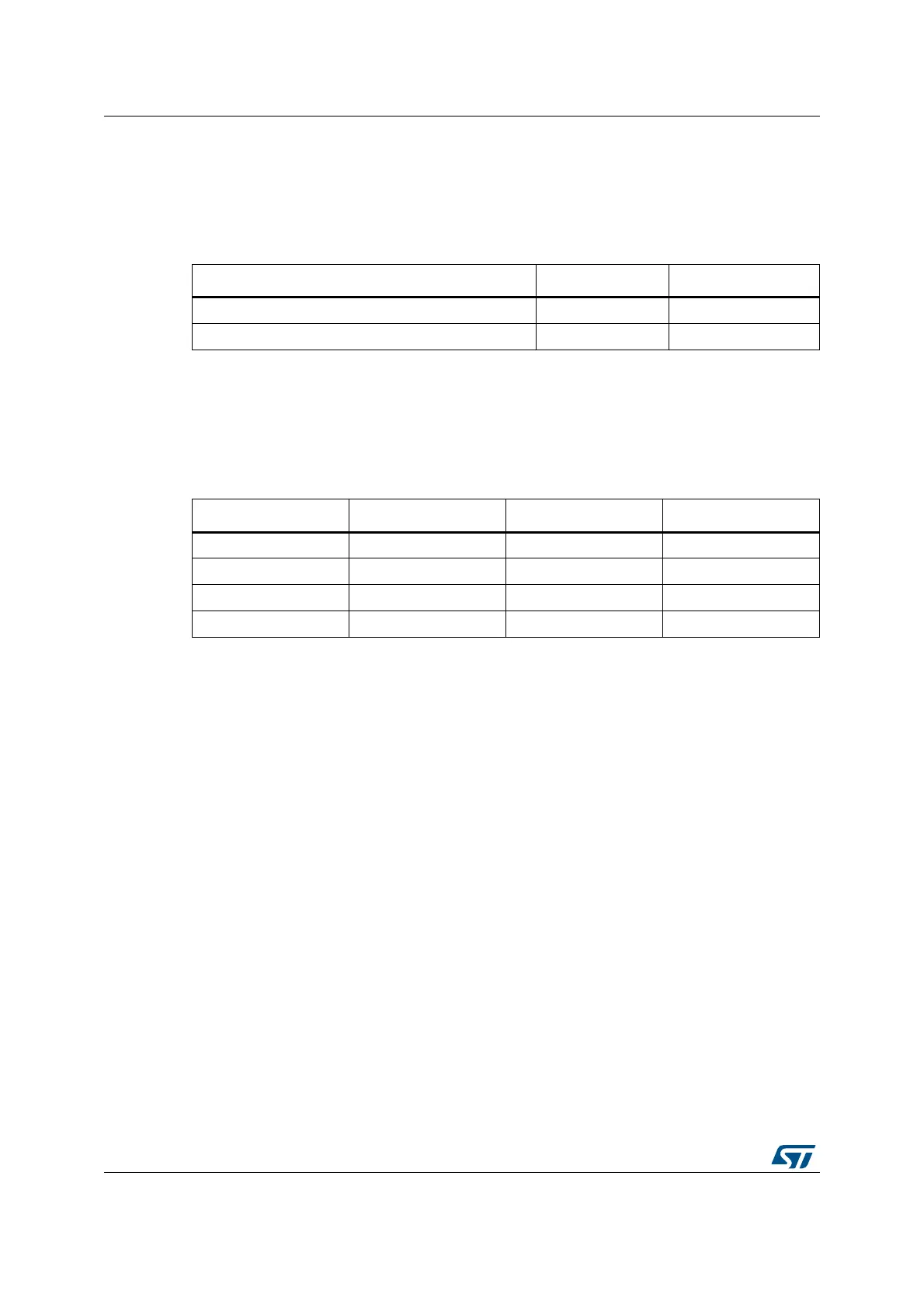

Table 183 summarizes the time required to process a 512-bit intermediate block for each

mode of operation.

The time required to process the last block of a message (or of a key in HMAC) can be

longer. This time depends on the length of the last block and the size of the key (in HMAC

mode).

Compared to the processing of an intermediate block, it can be increased by the factor

below:

• 1 to 2.5 for a hash message

• ~2.5 for an HMAC input-key

• 1 to 2.5 for an HMAC message

• ~2.5 for an HMAC output key in case of a short key

• 3.5 to 5 for an HMAC output key in case of a long key

Table 182. HASH interrupt requests

Interrupt event Event flag Enable control bit

Digest computation completed flag DCIS DCIE

Data input buffer ready to get a new block flag DINIS DINIE

Table 183. Processing time (in clock cycle)

Mode of operation FIFO load

(1)

1. The time required to load the 16 words of the block into the processor must be added to this value.

Computation phase Total

MD5 16 50 66

SHA-1 16 66 82

SHA-224 16 50 66

SHA-256 16 50 66

Loading...

Loading...