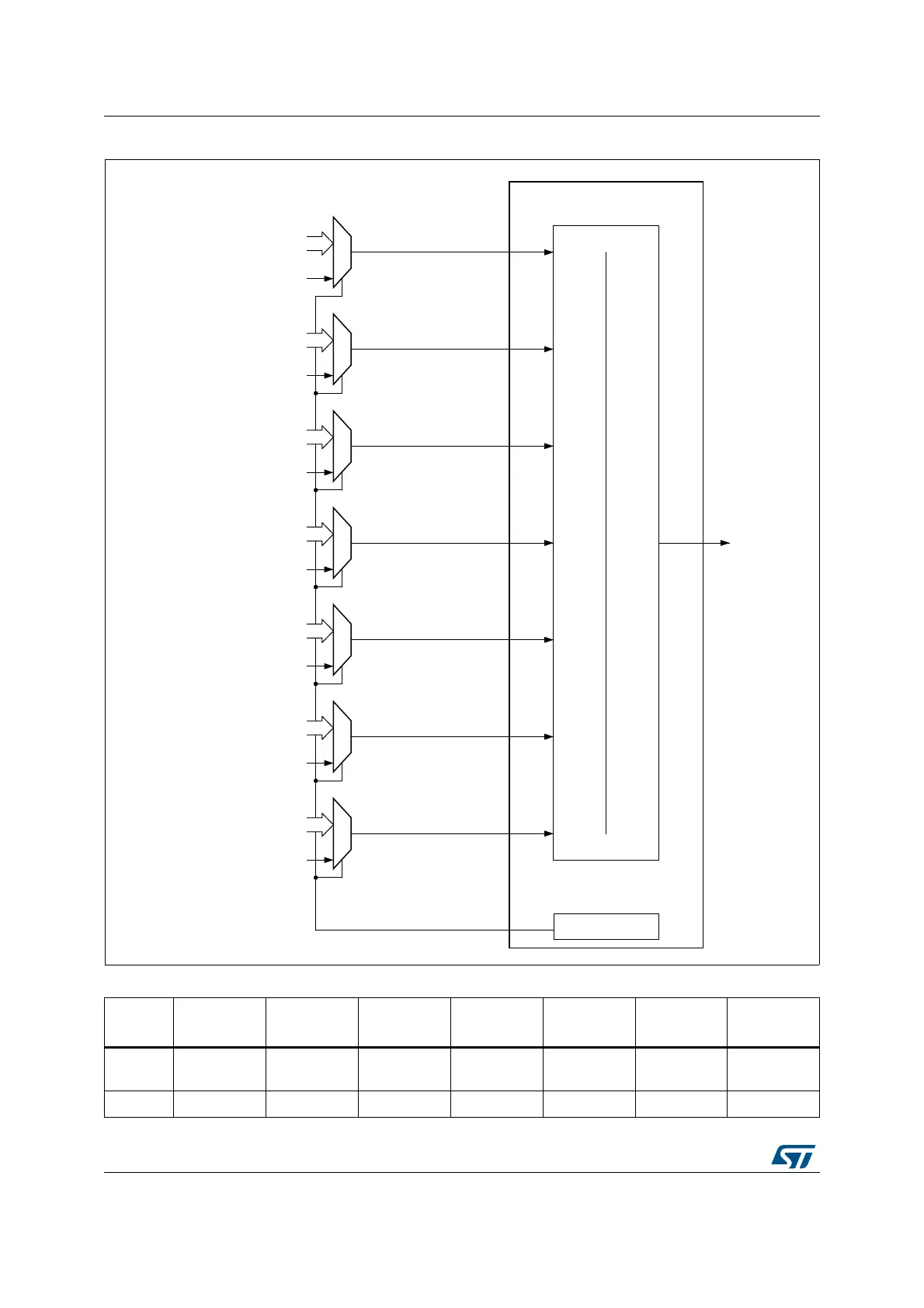

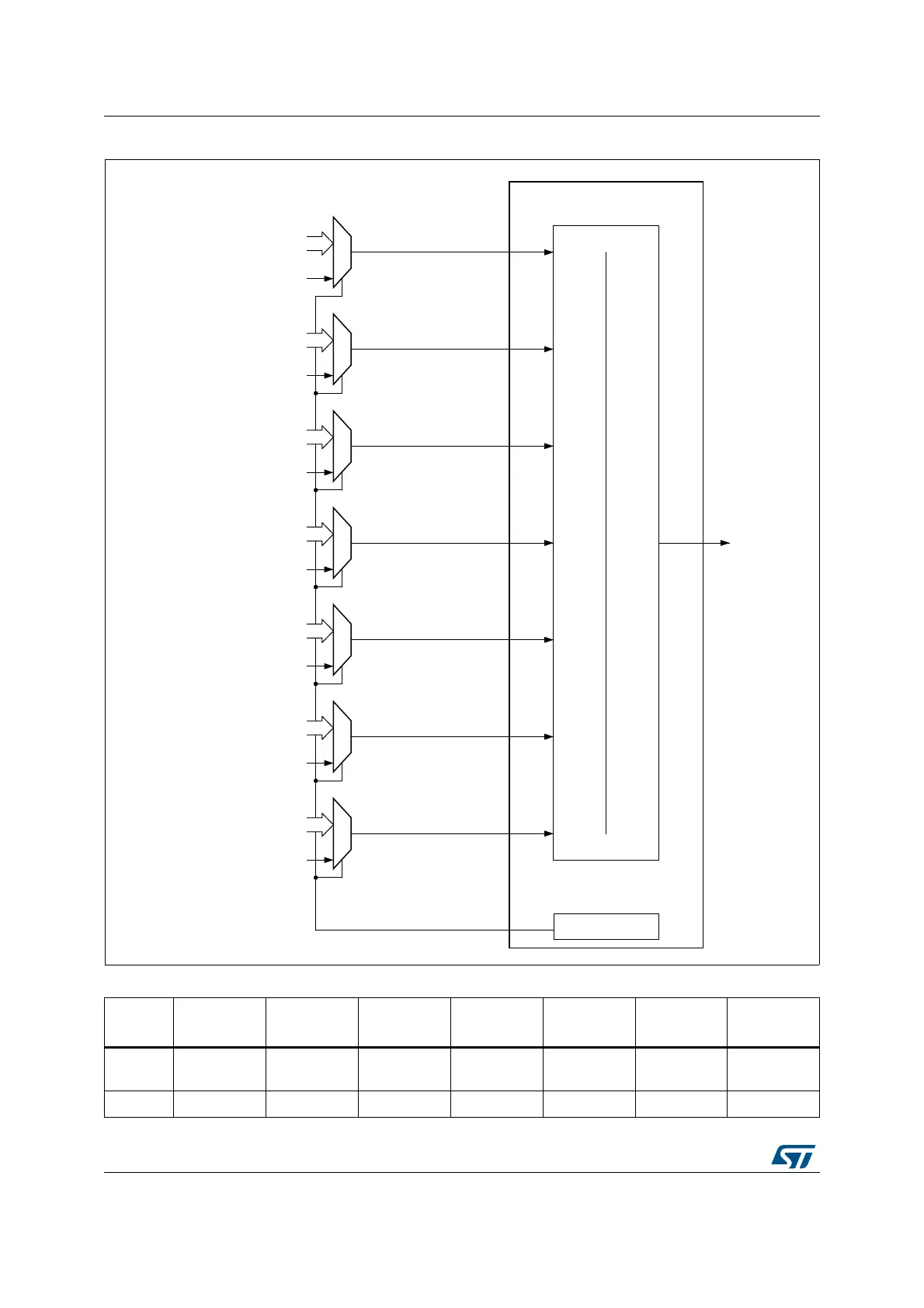

Figure 31. DMA2 request mapping

06Y9

+LJKSULRULW\

/RZSULRULW\

'0$B&6(/5

,&B5;6$,B$8$57B7;63,B5;

6:30,B5;7,0B&+7,0B75,*

$(6B,17,0B&+7,0B83

6:WULJJHU0(00(0ELW

&6

&KDQQHO

&KDQQHO

,&B7;6$,B%8$57B5;63,B7;

6:30,B7;7,0B&+7,0B83

$(6B2877,0B&+7,0B75,*

7,0B&20

6:WULJJHU0(00(0ELW

&6

&KDQQHO

$'&6$,B$8$57B7;63,B5;

$(6B287

6:WULJJHU0(00(0ELW

&6

&KDQQHO

$'&6$,B%7,0B83'$&63,B7;

7,0B&+6'00&

6:WULJJHU0(00(0ELW

&6

&KDQQHO

$'&8$57B5;7,0B83'$&

'&0,7,0B&+$(6B,16'00&

6:WULJJHU0(00(0ELW

&6

&KDQQHO

'&0,6$,B$86$57B7;/38$57B7;

,&B5;7,0B&+

6:WULJJHU0(00(0ELW

&6

&KDQQHO

6$,B%86$57B5;48$'63,

/38$57B5;,&B7;+$6+B,1

7,0B&+

6:WULJJHU0(00(0ELW

&6

3HULSKHUDOUHTXHVWVLJQDOV )L[HGKDUGZDUHSULRULW\

,QWHUQDO'0$

UHTXHVW

'0$FKDQQHO

Request.

Loading...

Loading...