General-purpose timers (TIM2/TIM3/TIM4/TIM5) RM0351

1012/1830 DocID024597 Rev 5

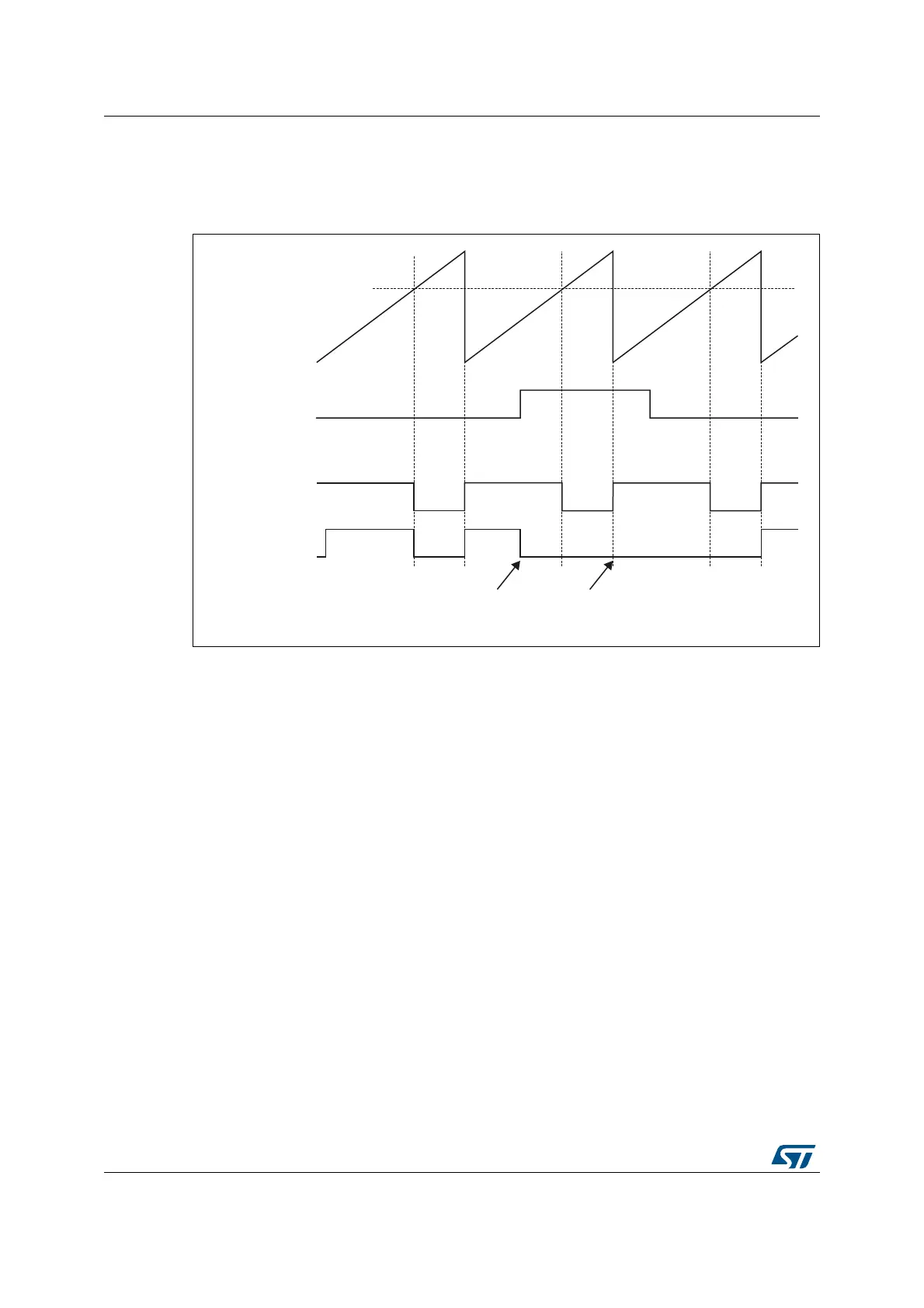

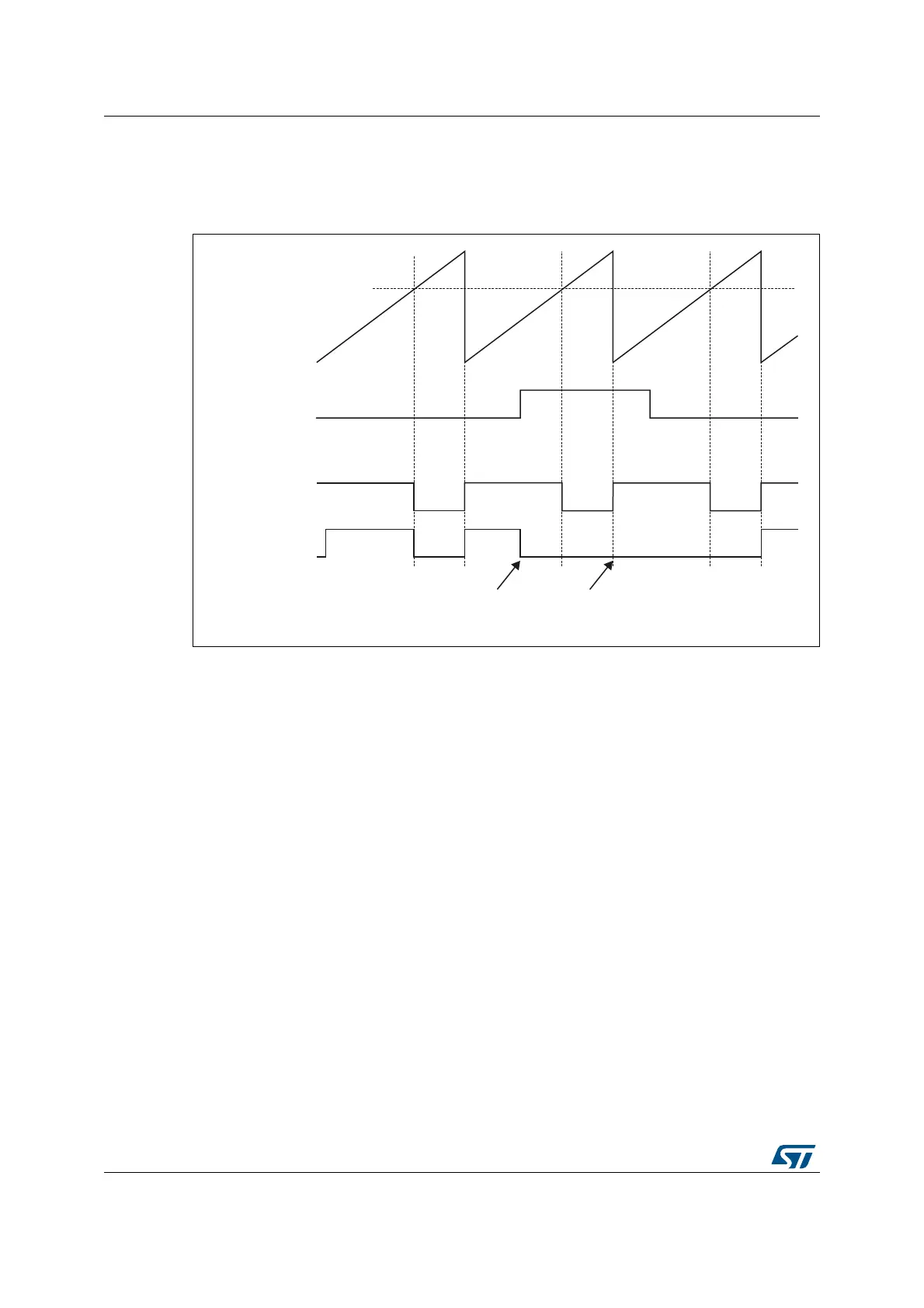

Figure 306 shows the behavior of the OCxREF signal when the ETRF input becomes high,

for both values of the OCxCE enable bit. In this example, the timer TIMx is programmed in

PWM mode.

Figure 306. Clearing TIMx OCxREF

Note: In case of a PWM with a 100% duty cycle (if CCRx>ARR), OCxREF is enabled again at the

next counter overflow.

069

&&5[

&RXQWHU&17

(75)

2&[5()

2&[&( µ¶

2&[5()

2&[&( µ¶

RFUHIBFOUBLQW

EHFRPHVKLJK

RFUHIBFOUBLQW

VWLOOKLJK

Loading...

Loading...