DocID024597 Rev 5 551/1830

RM0351 Analog-to-digital converters (ADC)

614

These thresholds are programmed in bits HT1[11:0] and LT1[11:0] of the ADC_TR1 register

for the analog watchdog 1. When converting data with a resolution of less than 12 bits

(according to bits RES[1:0]), the LSB of the programmed thresholds must be kept cleared

because the internal comparison is always performed on the full 12-bit raw converted data

(left aligned).

Table 112 describes how the comparison is performed for all the possible resolutions for

analog watchdog 1.

Description of analog watchdog 2 and 3

The second and third analog watchdogs are more flexible and can guard several selected

channels by programming the corresponding bits in AWDCHx[19:0] (x=2,3).

The corresponding watchdog is enabled when any bit of AWDCHx[19:0] (x=2,3) is set.

They are limited to a resolution of 8 bits and only the 8 MSBs of the thresholds can be

programmed into HTx[7:0] and LTx[7:0]. Table 113 describes how the comparison is

performed for all the possible resolutions.

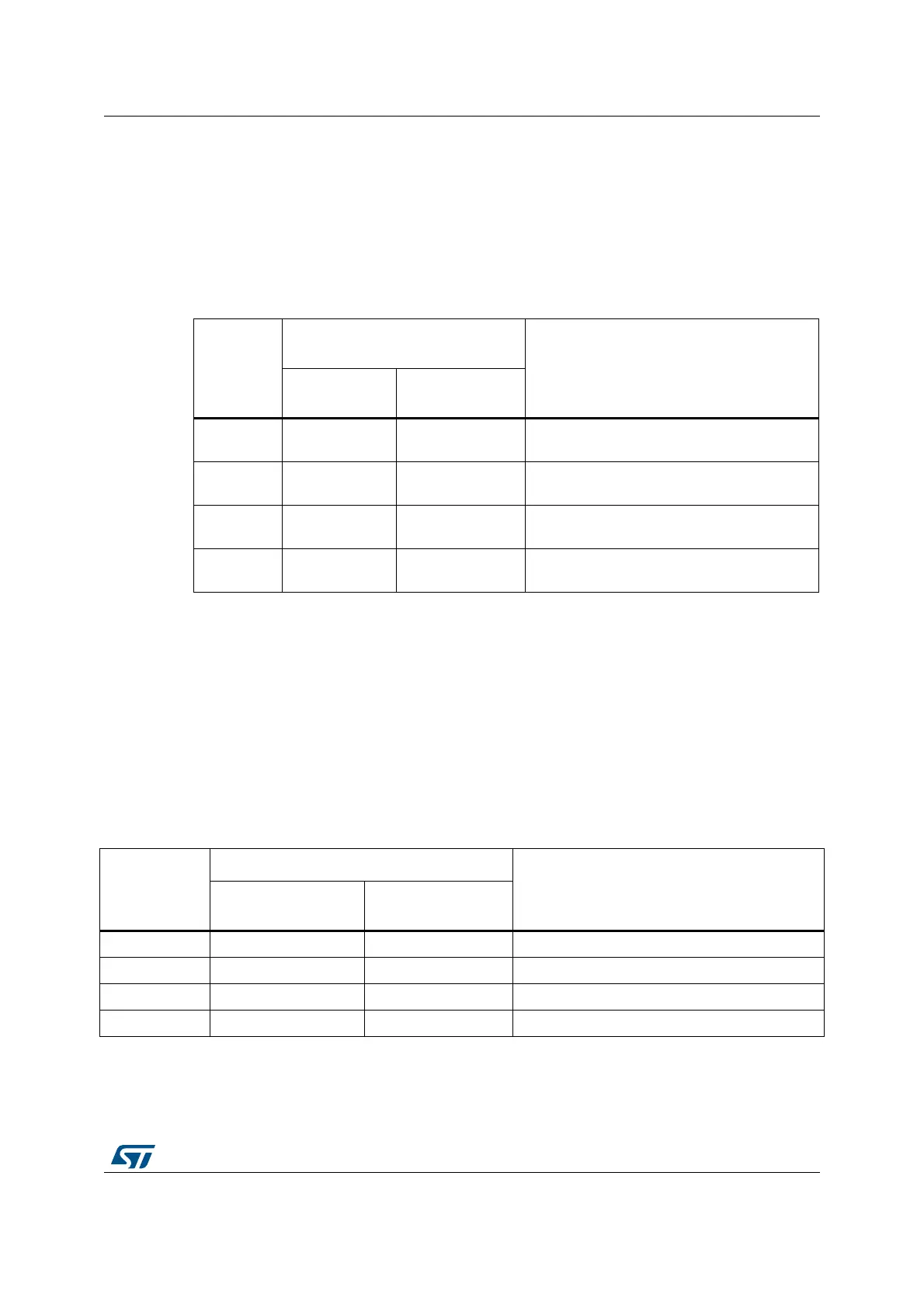

Table 112. Analog watchdog 1 comparison

Resolution

(bit

RES[1:0])

Analog watchdog comparison

between:

Comments

Raw converted data,

left aligned

(1)

1. The watchdog comparison is performed on the raw converted data before any alignment calculation and

before applying any offsets (the data which is compared is not signed).

Thresholds

00: 12-bit DATA[11:0]

LT1[11:0] and

HT1[11:0]

-

01: 10-bit DATA[11:2],00

LT1[11:0] and

HT1[11:0]

User must configure LT1[1:0] and HT1[1:0] to

00

10: 8-bit DATA[11:4],0000

LT1[11:0] and

HT1[11:0]

User must configure LT1[3:0] and HT1[3:0] to

0000

11: 6-bit

DATA[11:6],0000

00

LT1[11:0] and

HT1[11:0]

User must configure LT1[5:0] and HT1[5:0] to

000000

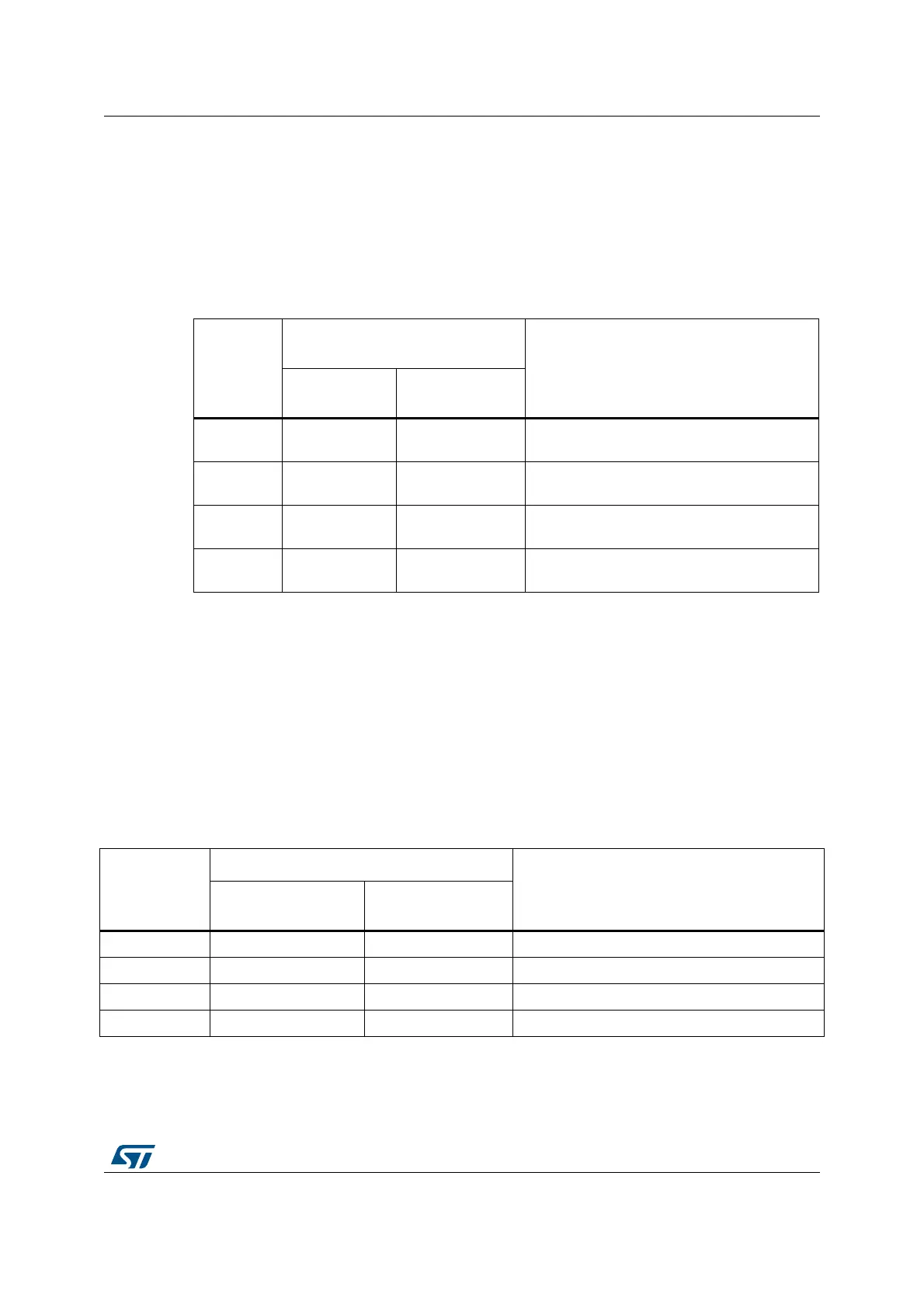

Table 113. Analog watchdog 2 and 3 comparison

Resolution

(bits RES[1:0])

Analog watchdog comparison between:

Comments

Raw converted data,

left aligned

(1)

Thresholds

00: 12-bit DATA[11:4] LTx[7:0] and HTx[7:0] DATA[3:0] are not relevant for the comparison

01: 10-bit DATA[11:4] LTx[7:0] and HTx[7:0] DATA[3:2] are not relevant for the comparison

10: 8-bit DATA[11:4] LTx[7:0] and HTx[7:0] -

11: 6-bit DATA[11:6],00 LTx[7:0] and HTx[7:0] User must configure LTx[1:0] and HTx[1:0] to 00

1. The watchdog comparison is performed on the raw converted data before any alignment calculation and before

applying any offsets (the data which is compared is not signed).

Loading...

Loading...