Analog-to-digital converters (ADC) RM0351

566/1830 DocID024597 Rev 5

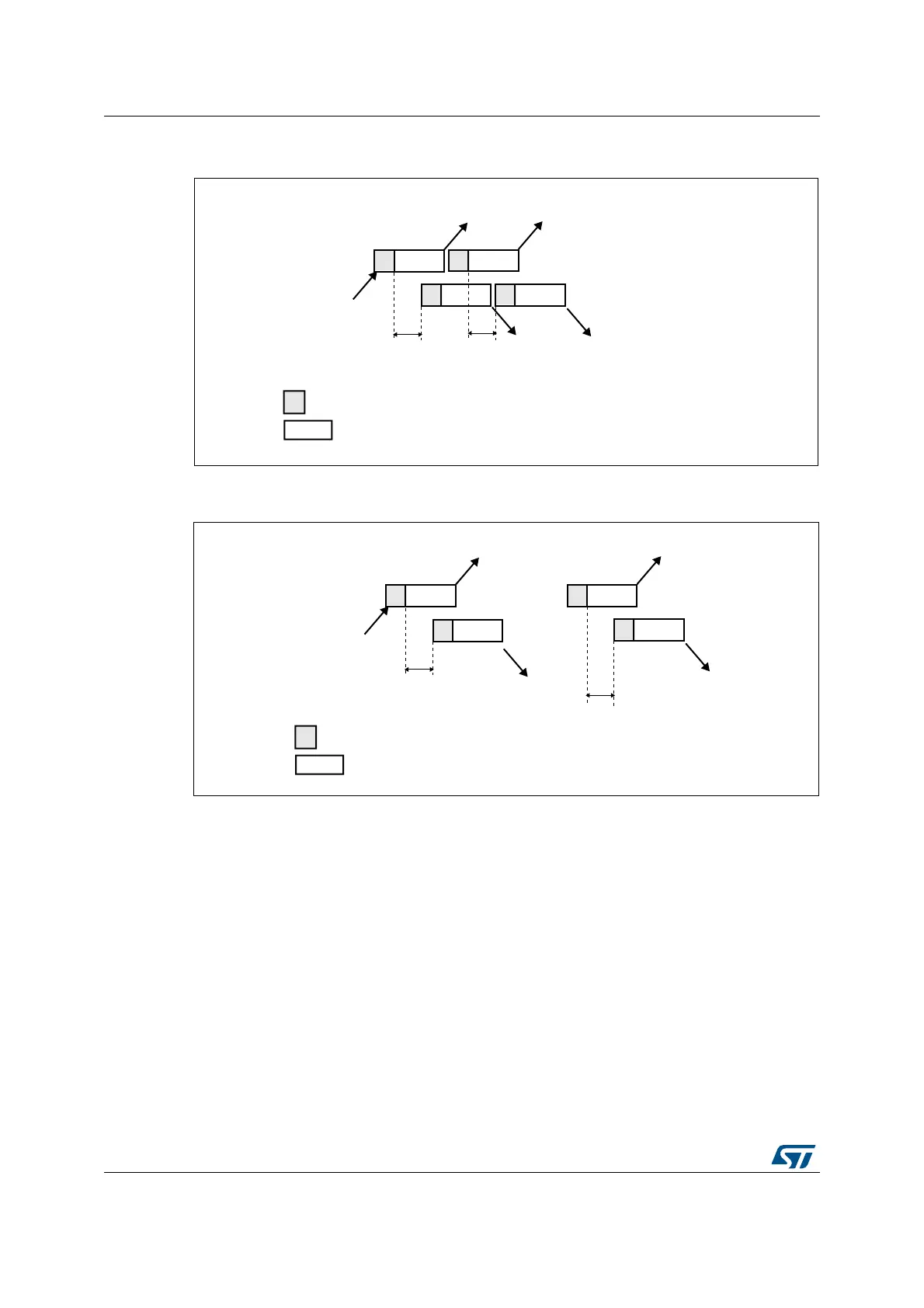

Figure 121. Interleaved mode on 1 channel in continuous conversion mode: dual ADC

mode

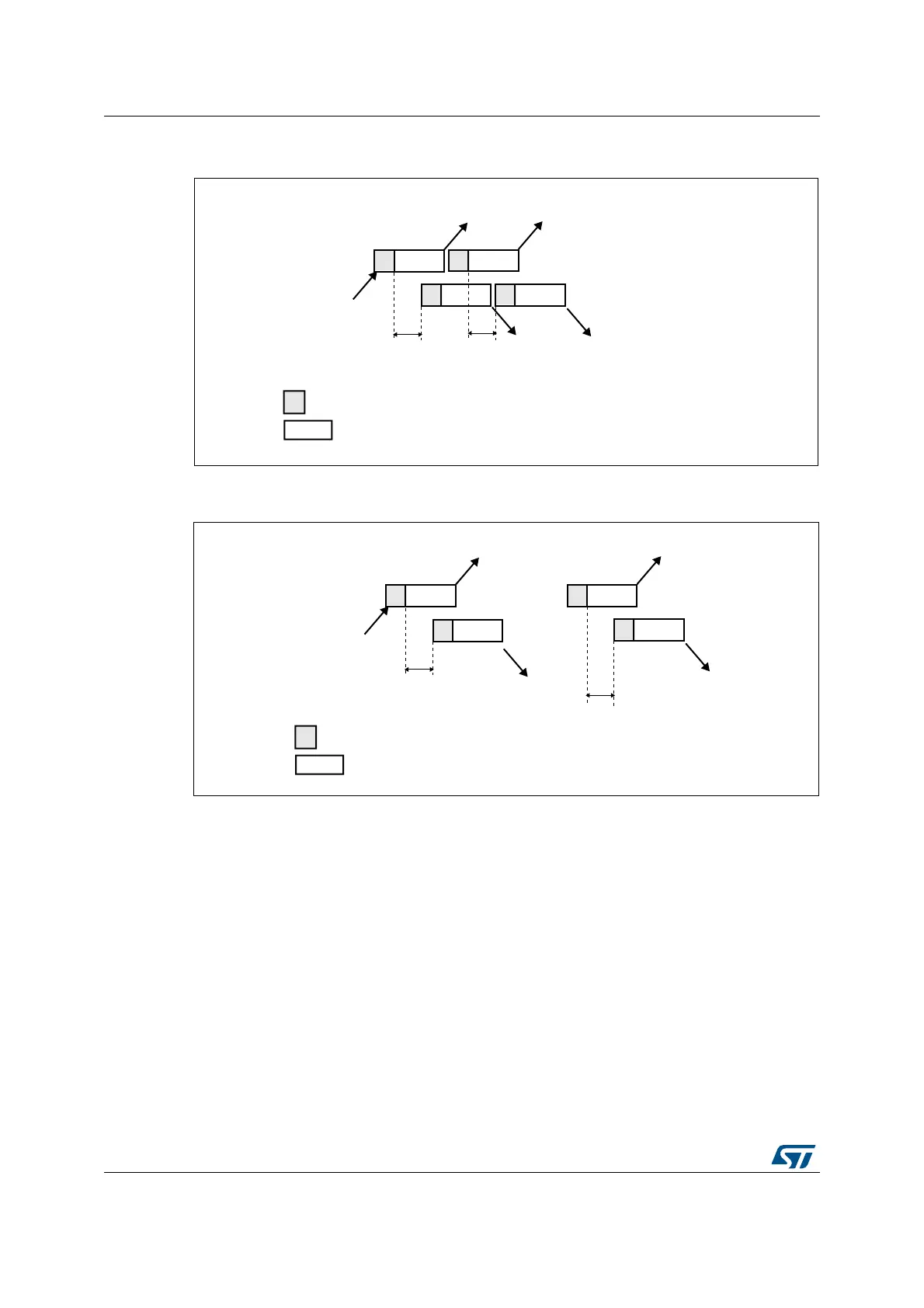

Figure 122. Interleaved mode on 1 channel in single conversion mode: dual ADC

mode

If DISCEN=1, each “n” simultaneous conversions (“n” is defined by DISCNUM) of the

regular sequence require a regular trigger event to occur.

In this mode, injected conversions are supported. When injection is done (either on master

or on slave), both the master and the slave regular conversions are aborted and the

sequence is re-started from the master (see Figure 123 below).

-36

0$67(5$'&

7ULJJHU

&+

6DPSOLQJ

&RQYHUVLRQ

&+

$'&&/.

F\FOHV

&+

&+

$'&&/.

F\FOHV

6/$9($'&

(QGRIFRQYHUVLRQRQVODYH$'&

(QGRIFRQYHUVLRQRQPDVWHU$'&

069

0$67(5$'&

7ULJJHU

&+

6DPSOLQJ

&RQYHUVLRQ

&+

$'&&/.

F\FOHV

&+

&+

$'&&/.

F\FOHV

6/$9($'&

(QGRIFRQYHUVLRQ

RQVODYH$'&

(QGRIFRQYHUVLRQRQPDVWHU$'&

(QGRIFRQYHUVLRQ

RQVODYH$'&

Loading...

Loading...