Flexible static memory controller (FSMC) RM0351

420/1830 DocID024597 Rev 5

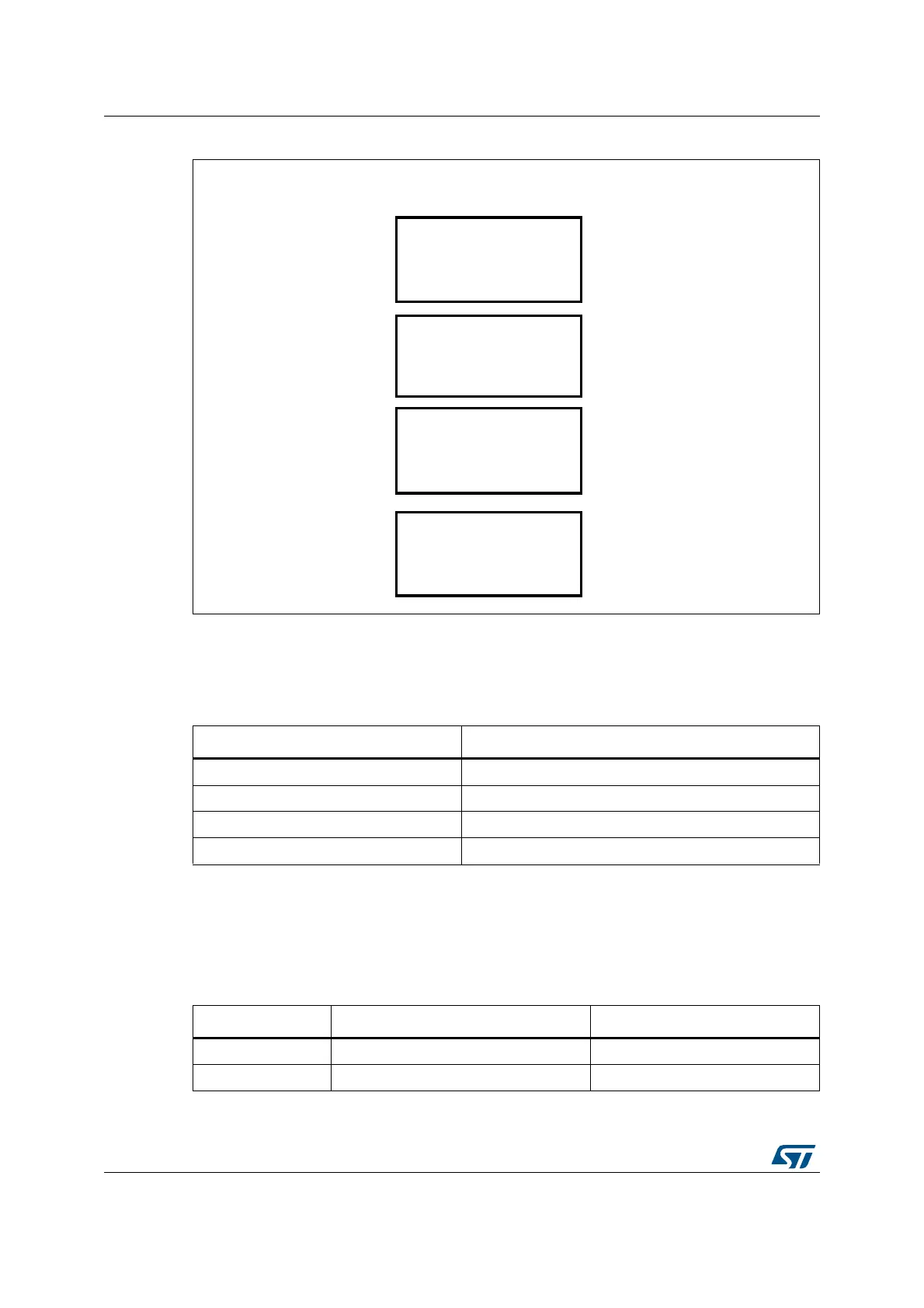

Figure 37. FMC memory banks

16.4.1 NOR/PSRAM address mapping

HADDR[27:26] bits are used to select one of the four memory banks as shown in Table 62.

The HADDR[25:0] bits contain the external memory address. Since HADDR is a byte

address whereas the memory is addressed at word level, the address actually issued to the

memory varies according to the memory data width, as shown in the following table.

D^ϯϰϰϳϱsϭ

ĂŶŬϭ

ϰdžϲϰD

EKZW^ZD^ZD

^ƵƉƉŽƌƚĞĚŵĞŵŽƌLJƚLJƉĞ

ĂŶŬ

ϬdžϲϬϬϬϬϬϬϬ

ĚĚƌĞƐƐ

Ϭdžϲ&&&&&&&

ϬdžϳϬϬϬϬϬϬϬ

Ϭdžϳ&&&&&&&

ϬdžϴϬϬϬϬϬϬϬ

Ϭdžϴ&&&&&&&

ϬdžϵϬϬϬϬϬϬϬ

Ϭdžϵ&&&&&&&

ZĞƐĞƌǀĞĚ

ĂŶŬϯ

ϰdžϲϰD

ZĞƐĞƌǀĞĚ

EE&ůĂƐŚŵĞŵŽƌLJ

Table 62. NOR/PSRAM bank selection

HADDR[27:26]

(1)

1. HADDR are internal AHB address lines that are translated to external memory.

Selected bank

00 Bank 1 - NOR/PSRAM 1

01 Bank 1 - NOR/PSRAM 2

10 Bank 1 - NOR/PSRAM 3

11 Bank 1 - NOR/PSRAM 4

Table 63. NOR/PSRAM External memory address

Memory width

(1)

Data address issued to the memory Maximum memory capacity (bits)

8-bit HADDR[25:0] 64 Mbytes x 8 = 512 Mbit

16-bit HADDR[25:1] >> 1 64 Mbytes/2 x 16 = 512 Mbit

Loading...

Loading...