DocID024597 Rev 5 1493/1830

RM0351 Single Wire Protocol Master Interface (SWPMI)

1517

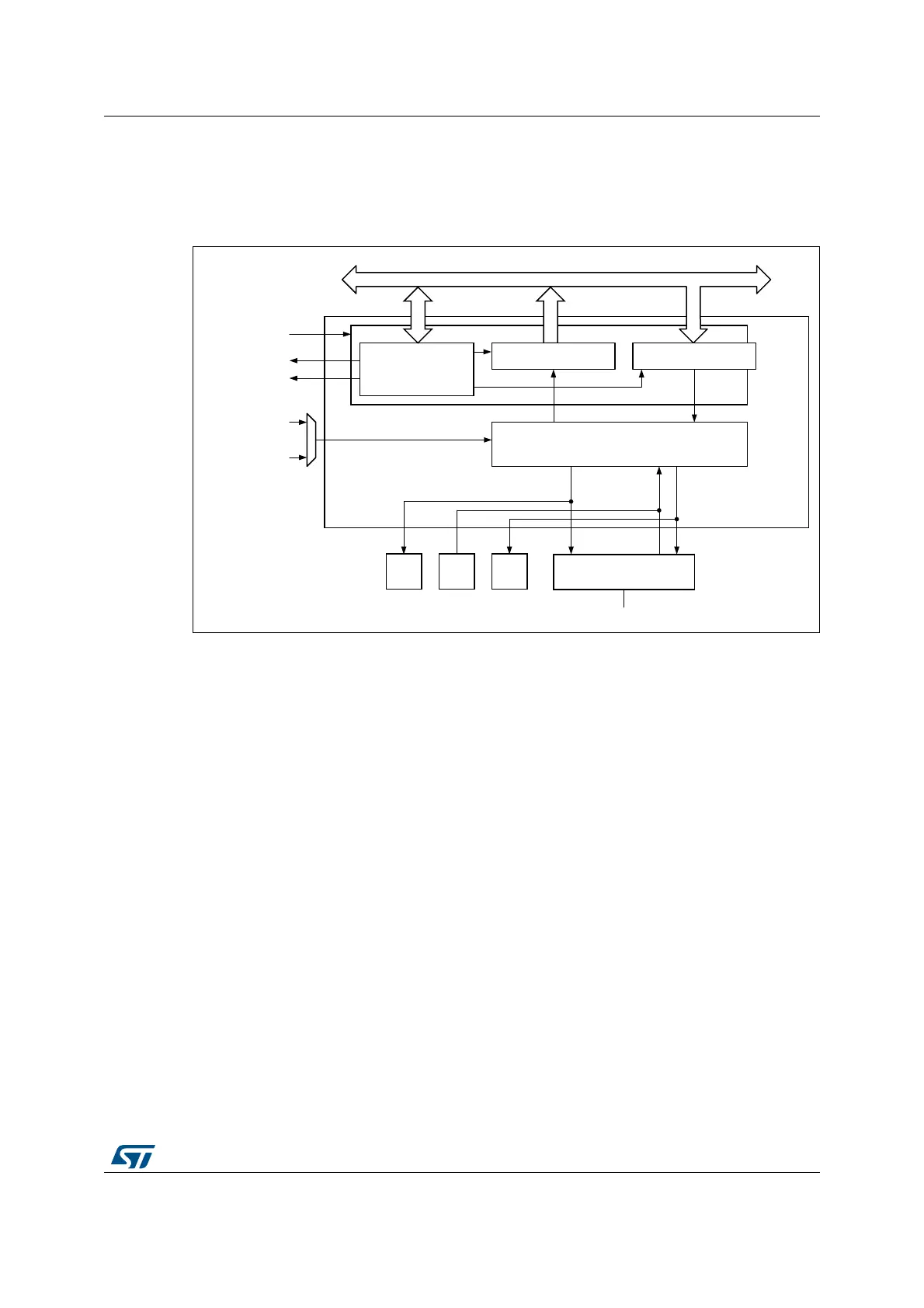

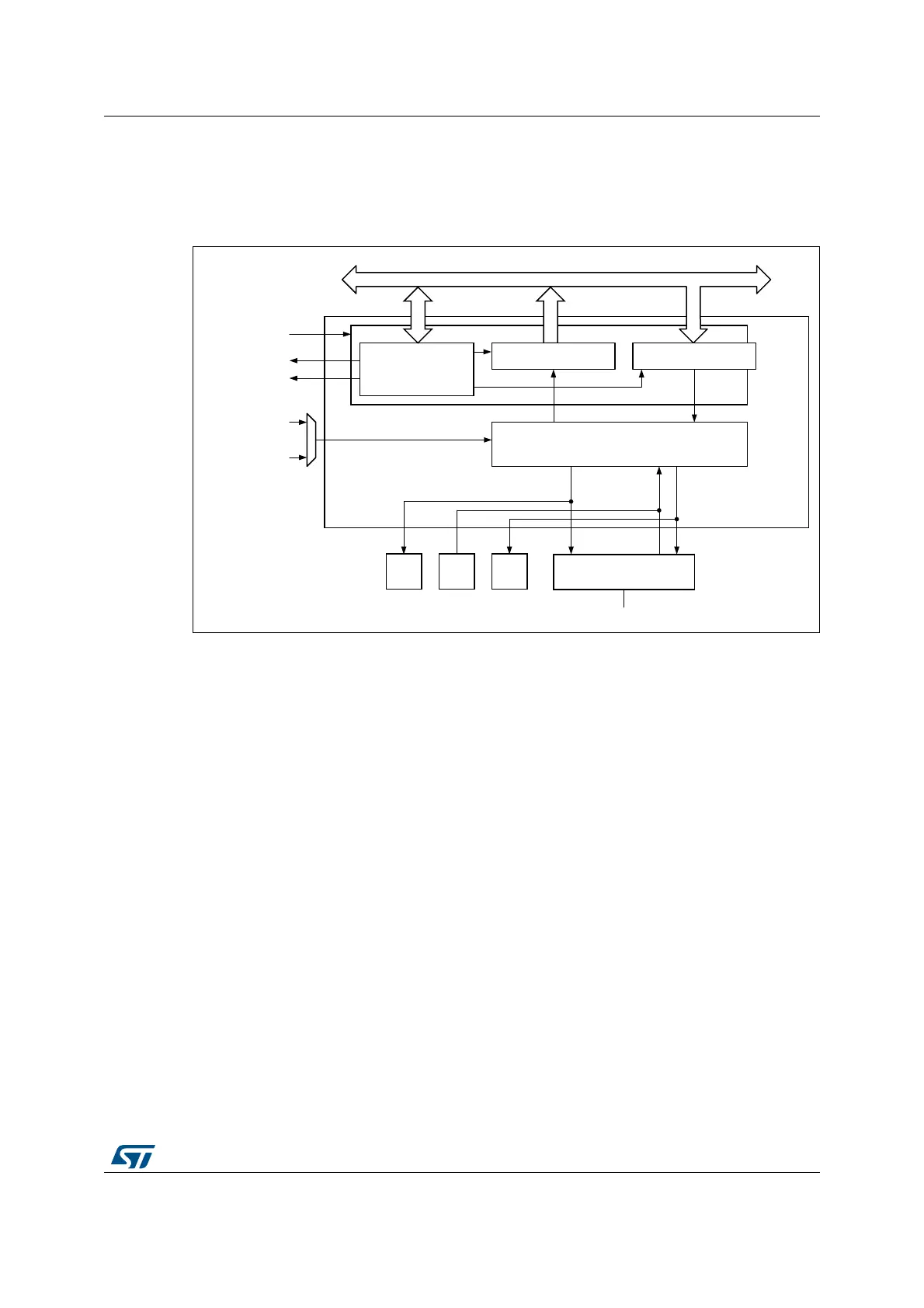

44.3 SWPMI functional description

44.3.1 SWPMI block diagram

Figure 477. SWPMI block diagram

Refer to the bit SWPMI1SEL in Section 6.4.28: Peripherals independent clock configuration

register (RCC_CCIPR) to select the SWPCLK (SWPMI core clock source).

Note: In order to support the exit from Stop mode by a RESUME by slave, it is mandatory to select

HSI16 for SWPCLK. If this feature is not required, PCLK1 can be selected, and SWPMI

must be disabled before entering the Stop mode.

44.3.2 SWP initialization and activation

The initialization and activation will set the SWPMI_IO state from low to high.

For Class B, i.e. V

DD

is in the range [2.70 V to 3.30 V], the procedure is the following:

1. clear the SWP_CLASS bit in SWPMI_OR register,

2. configure SWPMI_IO as alternate function (refer to Section 8: General-purpose I/Os

(GPIO)) to enable the SWPMI_IO transceiver,

3. wait for t

SWPSTART

Max (refer to product datasheet),

4. set SWPACT bit in SWPMI_CR register to ACTIVATE the SWP i.e. to move from

DEACTIVATED to SUSPENDED.

For Class C, i.e. V

DD

is in the range [1.62 V to 1.98 V], the procedure is the following:

1. set the SWP_CLASS bit in SWPMI_OR register,

2. configure SWPMI_IO as alternate function (refer to Section 8: General-purpose I/Os

(GPIO)) to enable the SWPMI_IO transceiver,

3. set SWPACT bit in SWPMI_CR register to ACTIVATE the SWP i.e. to move from

DEACTIVATED to SUSPENDED.

069

6:30,FRUH

6:30,B,2

3&/.

6:3&/.

'0$UHTXHVWV

3&/.

+6,

&RQWURO6WDWXV

UHJLVWHUV

6:3EXV

6:30,

6:30,B7;6:30,B5;

,QWHUUXSW

6:30,B6863(1'

*3,2*3,2*3,2

ELW$3%EXV

6:30,B7'56:30,B5'5

Loading...

Loading...