Quad-SPI interface (QUADSPI) RM0351

486/1830 DocID024597 Rev 5

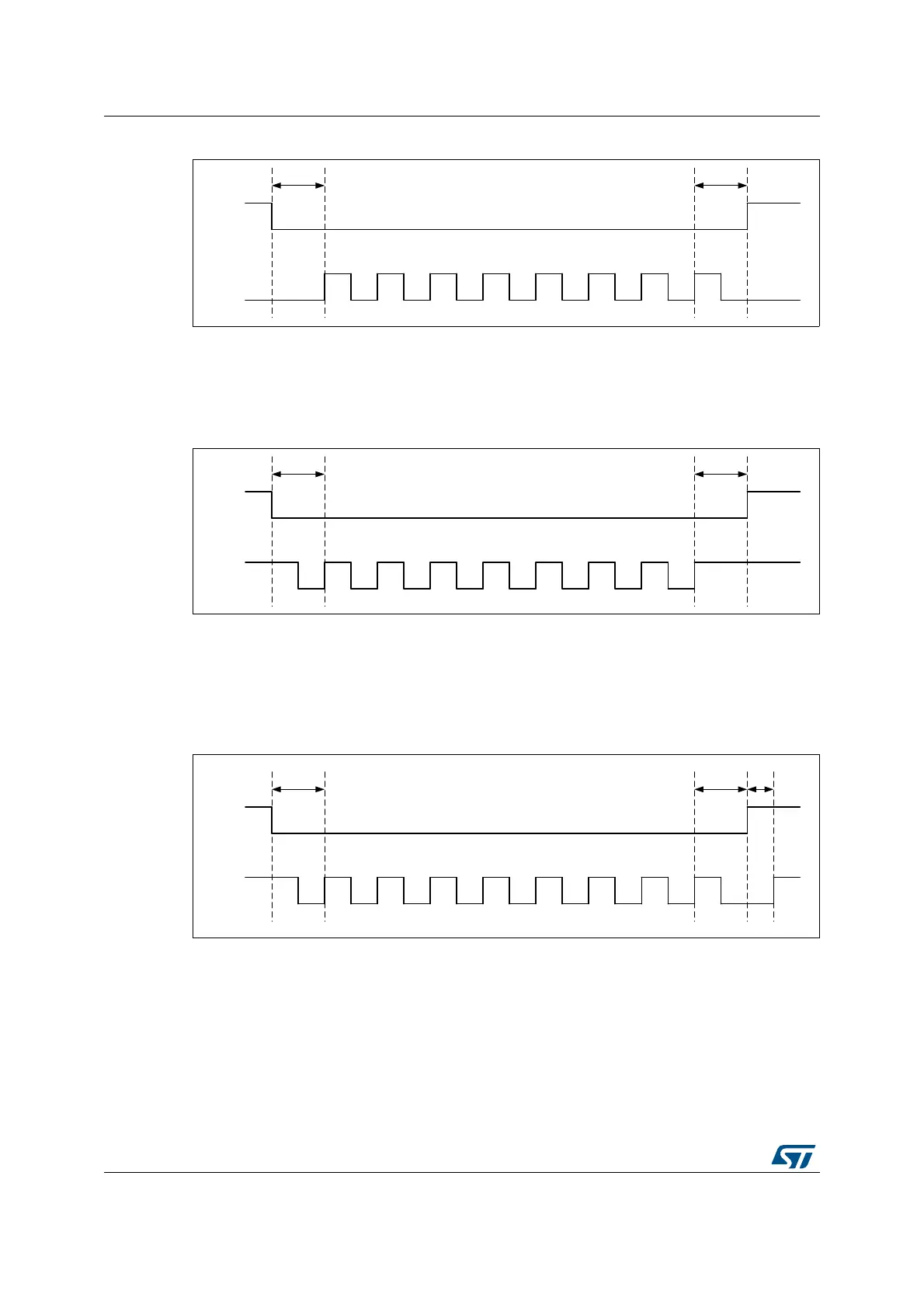

Figure 62. nCS when CKMODE = 0 (T = CLK period)

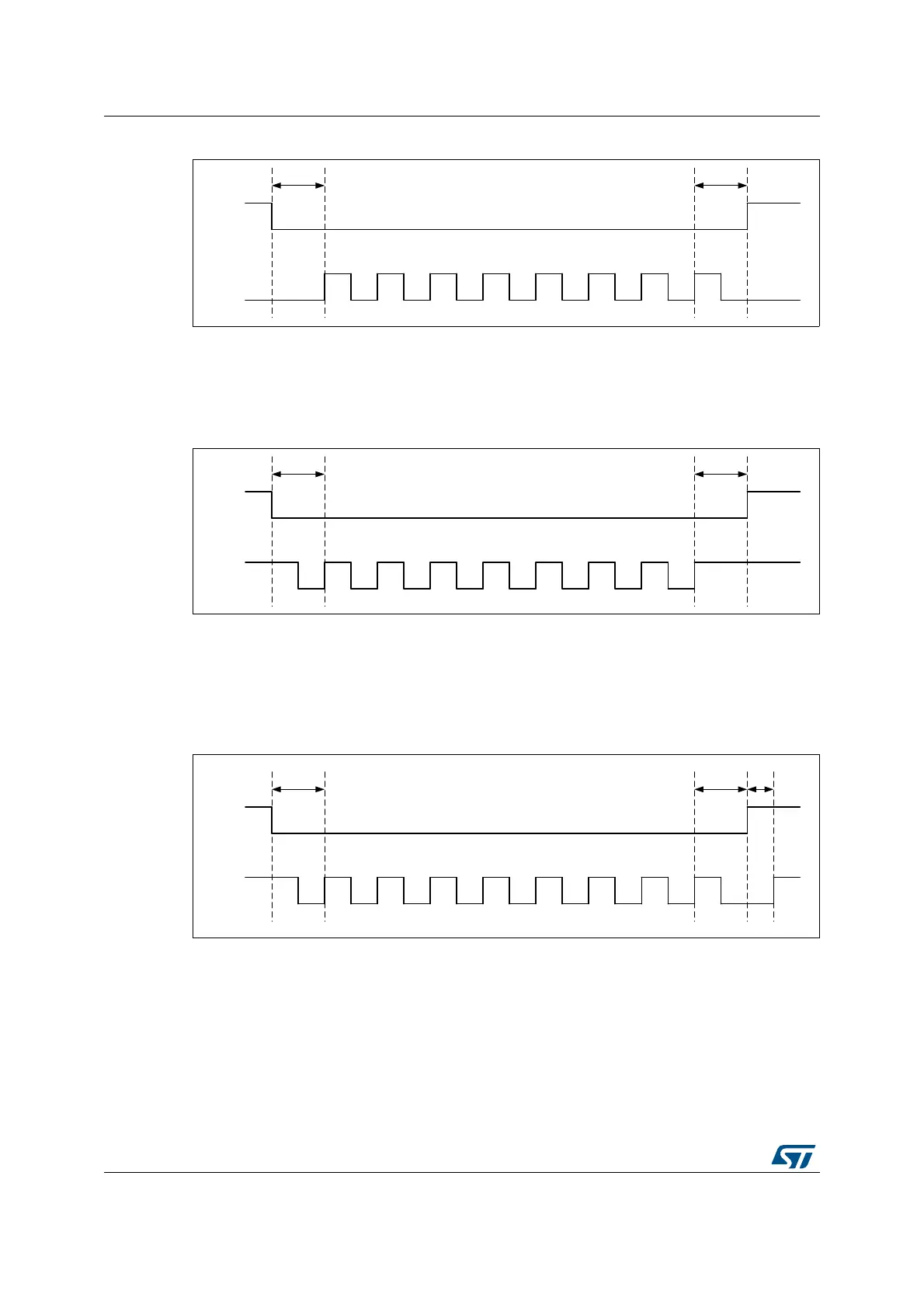

When CKMODE=1 (“mode3”, where CLK goes high when no operation is in progress) and

DDRM=0 (SDR mode), nCS still falls one CLK cycle before an operation first rising CLK

edge, and nCS rises one CLK cycle after the operation final rising CLK edge, as shown in

Figure 63.

Figure 63. nCS when CKMODE = 1 in SDR mode (T = CLK period)

When CKMODE = 1 (“mode3”) and DDRM = 1 (DDR mode), nCS falls one CLK cycle

before an operation first rising CLK edge, and nCS rises one CLK cycle after the operation

final active rising CLK edge, as shown in Figure 64. Because DDR operations must finish

with a falling edge, CLK is low when nCS rises, and CLK rises back up one half of a CLK

cycle afterwards.

Figure 64. nCS when CKMODE = 1 in DDR mode (T = CLK period)

When the FIFO stays full in a read operation or if the FIFO stays empty in a write operation,

the operation stalls and CLK stays low until firmware services the FIFO. If an abort occurs

when an operation is stalled, nCS rises just after the abort is requested and then CLK rises

one half of a CLK cycle later, as shown in Figure 65.

Loading...

Loading...