Single Wire Protocol Master Interface (SWPMI) RM0351

1502/1830 DocID024597 Rev 5

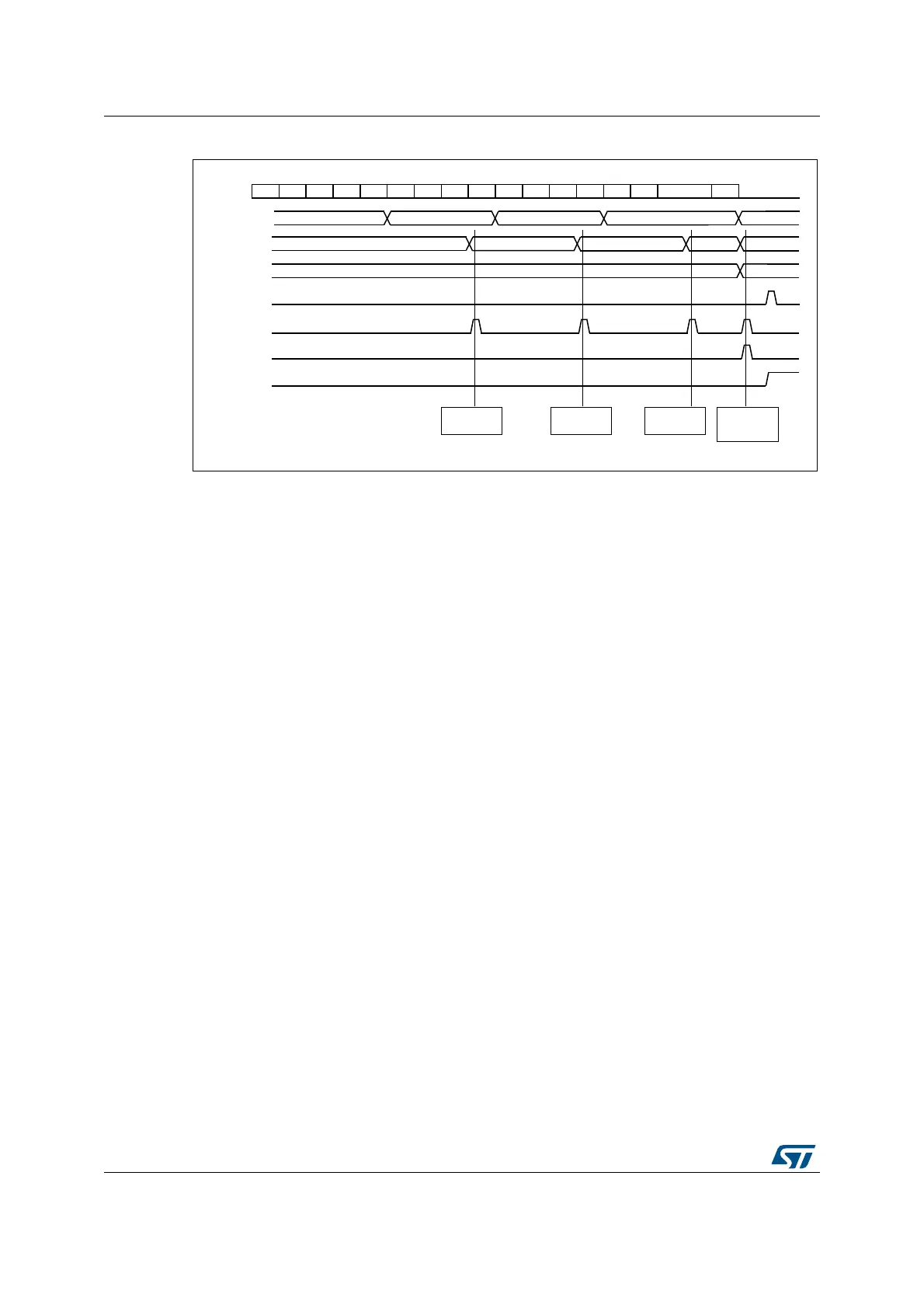

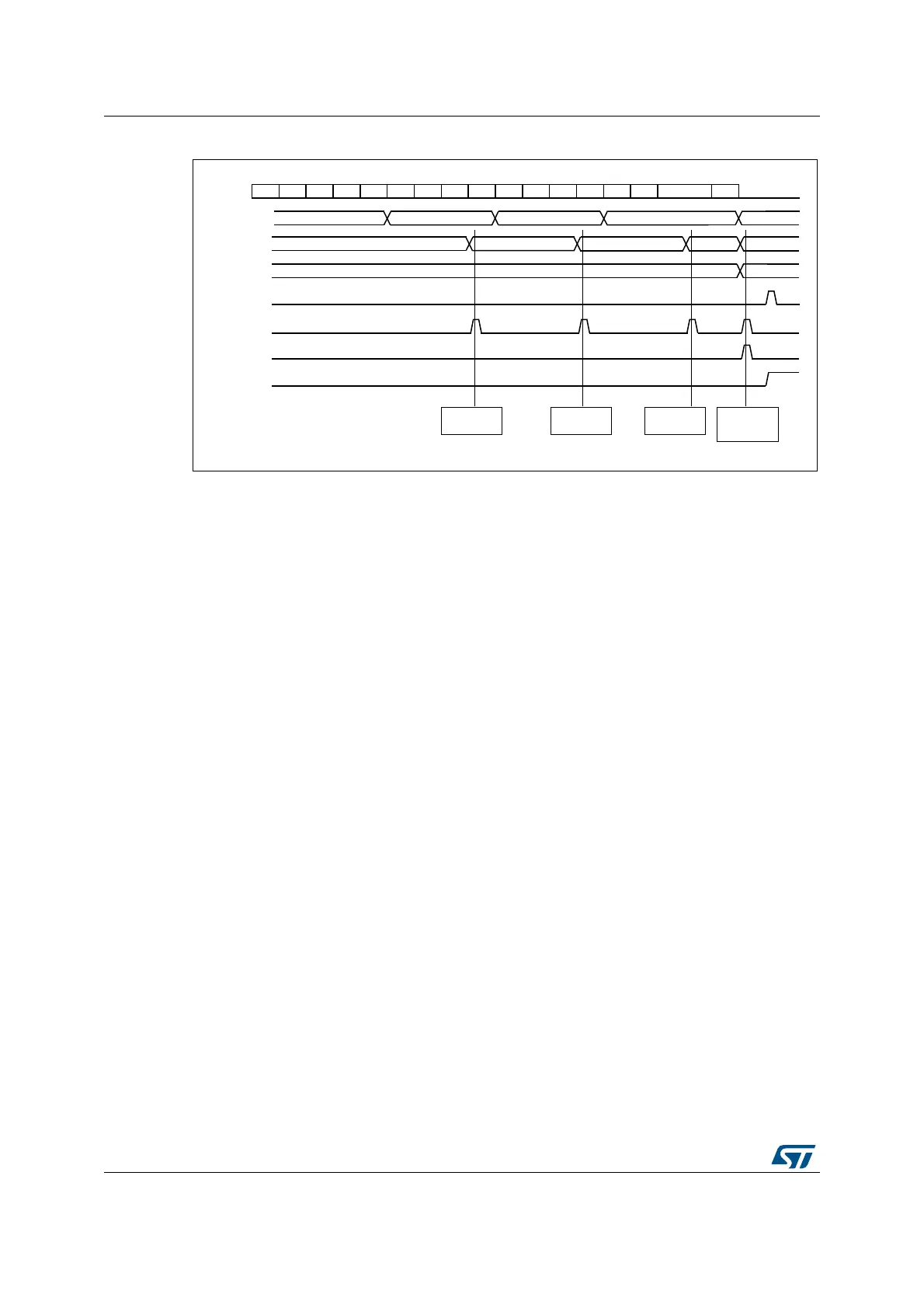

Figure 483. SWPMI No software buffer mode reception

Single software buffer mode

This mode allows to receive a complete SWP frame without any CPU intervention using the

DMA. The DMA transfers received data from the 32-bit SWPMI_RDR register to the RAM

memory, and the software can poll the end of the frame reception using the SWPMI_RBFF

flag.

The Single software buffer mode is selected by setting RXDMA bit and clearing RXMODE

bit in the SWPMI_CR register.

The DMA must be configured as follows:

The DMA channel or stream must be configured in following mode (refer to DMA section):

• memory to memory mode disabled,

• memory increment mode enabled,

• memory size set to 32-bit,

• peripheral size set to 32-bit,

• peripheral increment mode disabled,

• circular mode disabled,

• data transfer direction set to read from peripheral,

• the number of words to be transfered must be set to 8,

• the source address is the SWPMI_RDR register,

• the destination address is the SWP frame buffer in RAM.

Then the user must:

1. Set RXDMA bit in the SWPMI_CR register

2. Set RXBFIE bit in the SWPMI_IER register

3. Enable stream or channel in DMA module.

A DMA request is issued by SWPMI when RXNE flag is set in SWPMI_ISR. The RXNE flag

is cleared automatically when the DMA is reading the SWPMI_RDR register.

In the SWPMI interrupt routine, the user must check RXBFF bit in the SWPMI_ISR register.

If it is set, the user must:

069

62) (2)&5&' ' ' ' ' ' ' ' ' ' ' ' '

6:3

LQSXW

5;1(

6:30,B5'5

5;%))

VHWE\+:FOHDUHGE\6:RU'0$

'''' ''''

''

''

[[''

[[[[

dž G

6:30,B5)/

'

VHWE\+:FOHDUHGE\6:

6863(1'

6:UHDGV

6:30,B5'5

7&)

VHWE\+:FOHDUHGE\6:

6:UHDGV

6:30,B5'5

6:UHDGV

6:30,B5'5

6:UHDGV

6:30,B5'5

DQG6:,B5)/

VHWE\+:

,QWHUQDOEXIIHU

'''' '''' ''''

[[[[

[[''

Loading...

Loading...