Power control (PWR) RM0351

164/1830 DocID024597 Rev 5

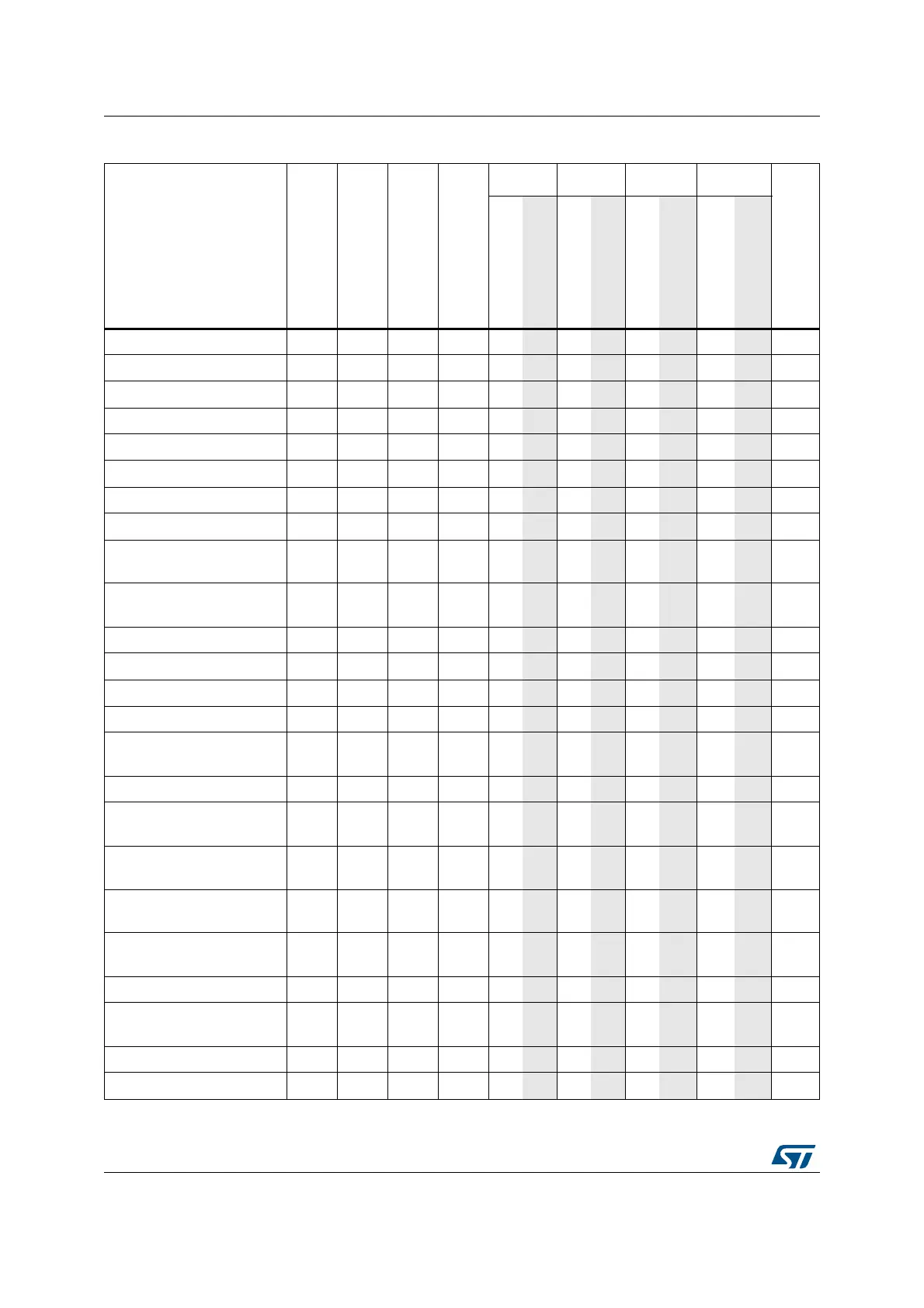

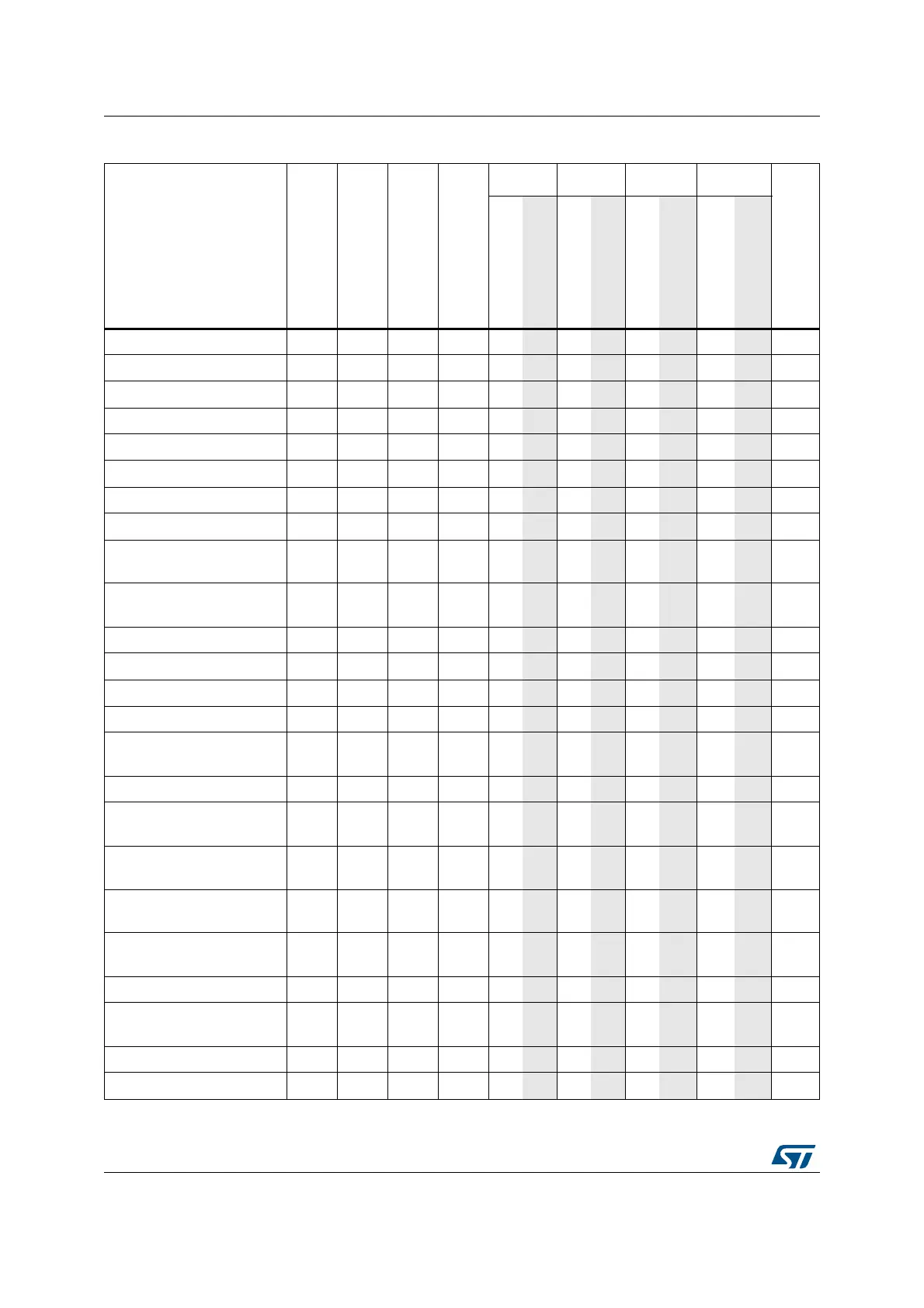

Table 23. Functionalities depending on the working mode

(1)

Peripheral Run Sleep

Low-power run

Low-power sleep

Stop 0/1 Stop 2 Standby Shutdown

VBAT

-

Wakeup capability

-

Wakeup capability

-

Wakeup capability

-

Wakeup capability

CPU Y - Y - - ---- ----

Flash memory (up to 1 MB) O

(2)

O

(2)

O

(2)

O

(2)

- ---- ----

SRAM1 (up to 256 KB) Y Y

(3)

YY

(3)

Y -Y-- ----

SRAM2 (up to 64 KB) Y Y

(3)

YY

(3)

Y -Y-O

(4)

----

FSMC OOOO-

---- ----

QUADSPI O O O O -

---- ----

Backup Registers YYYYY

-Y-Y -Y-Y

Brown-out reset (BOR) YYYYY

YYYY Y- --

Programmable Voltage

Detector (PVD)

OOOOOOOO- ----

Peripheral Voltage Monitor

(PVMx; x=1,2,3,4)

OOOOO

OOO- ----

DMA O O O O - ---- ----

DMA2D O O O O -

---- ----

Oscillator HSI16 O O O O

(5)

-

(5)

-- ----

Oscillator HSI48 O O - - -

---- ----

High Speed External (HSE) O O O O - ---- ----

Low Speed Internal (LSI) O O O O O

-O-O----

Low Speed External (LSE) O O O O O -O-O -O-O

Multi-Speed Internal (MSI) O O O O -

---- ----

Clock Security System

(CSS)

OOOO-

---- ----

Clock Security System on

LSE

OOOOO

OOOO O- --

RTC / Auto wakeup O O O O O OOOO OOOO

Number of RTC Tamper

pins

33333O3O3O3O3

Camera interface O O O O -

---- ----

LCD O O O O O

OOO- ----

Loading...

Loading...