DocID024597 Rev 5 87/1830

RM0351

92

The write protection can be enabled in SYSCFG SRAM2 write protection register

(SYSCFG_SWPR) in the SYSCFG block. This is a register with write ‘1’ once mechanism,

which means by writing ‘1’ on a bit it will setup the write protection for that page of SRAM

and it can be removed/cleared by a system reset only.

2.4.3 SRAM2 Read protection

The SRAM2 is protected with the Read protection (RDP). Refer to Section 3.5.1: Read

protection (RDP) for more details.

2.4.4 SRAM2 Erase

The SRAM2 can be erased with a system reset using the option bit SRAM2_RST in the user

option byte (refer to Section 3.4.1: Option bytes description).

The SRAM2 erase can also be requested by software by setting the bit SRAM2ER in the

SYSCFG SRAM2 control and status register (SYSCFG_SCSR).

2.5 Flash memory overview

The Flash memory is composed of two distinct physical areas:

• The main Flash memory block. It contains the application program and user data if

necessary.

• The information block. It is composed of three parts:

– Option bytes for hardware and memory protection user configuration.

– System memory that contains the proprietary boot loader code.

– OTP (one-time programmable) area

The Flash interface implements instruction access and data access based on the AHB

protocol. It implements a system of instruction prefetch and caches lines that speeds up

CPU code execution. It also implements the logic necessary to carry out the Flash memory

operations (Program/Erase) controlled through the Flash registers. Refer to Section 3:

Embedded Flash memory (FLASH) for more details.

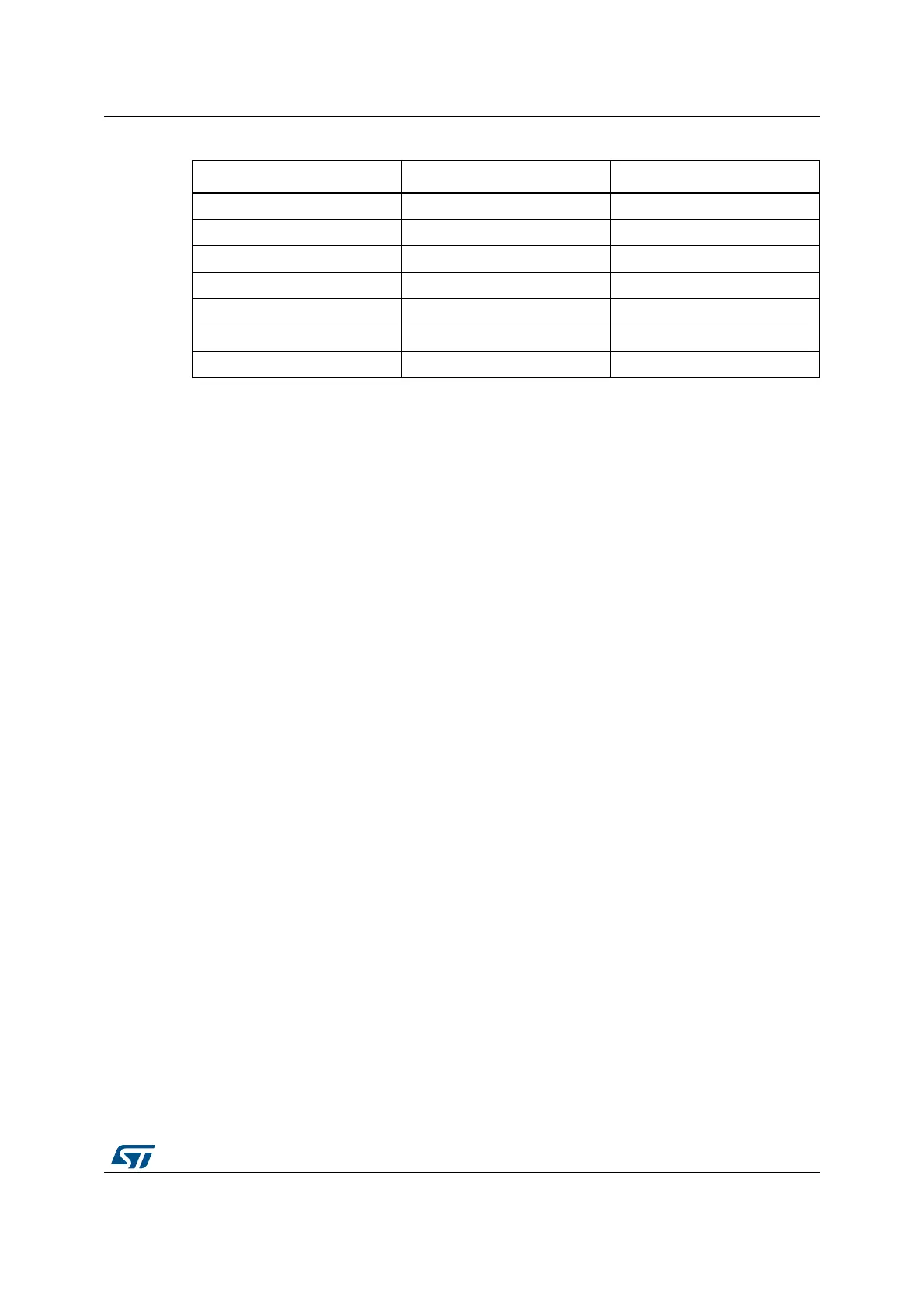

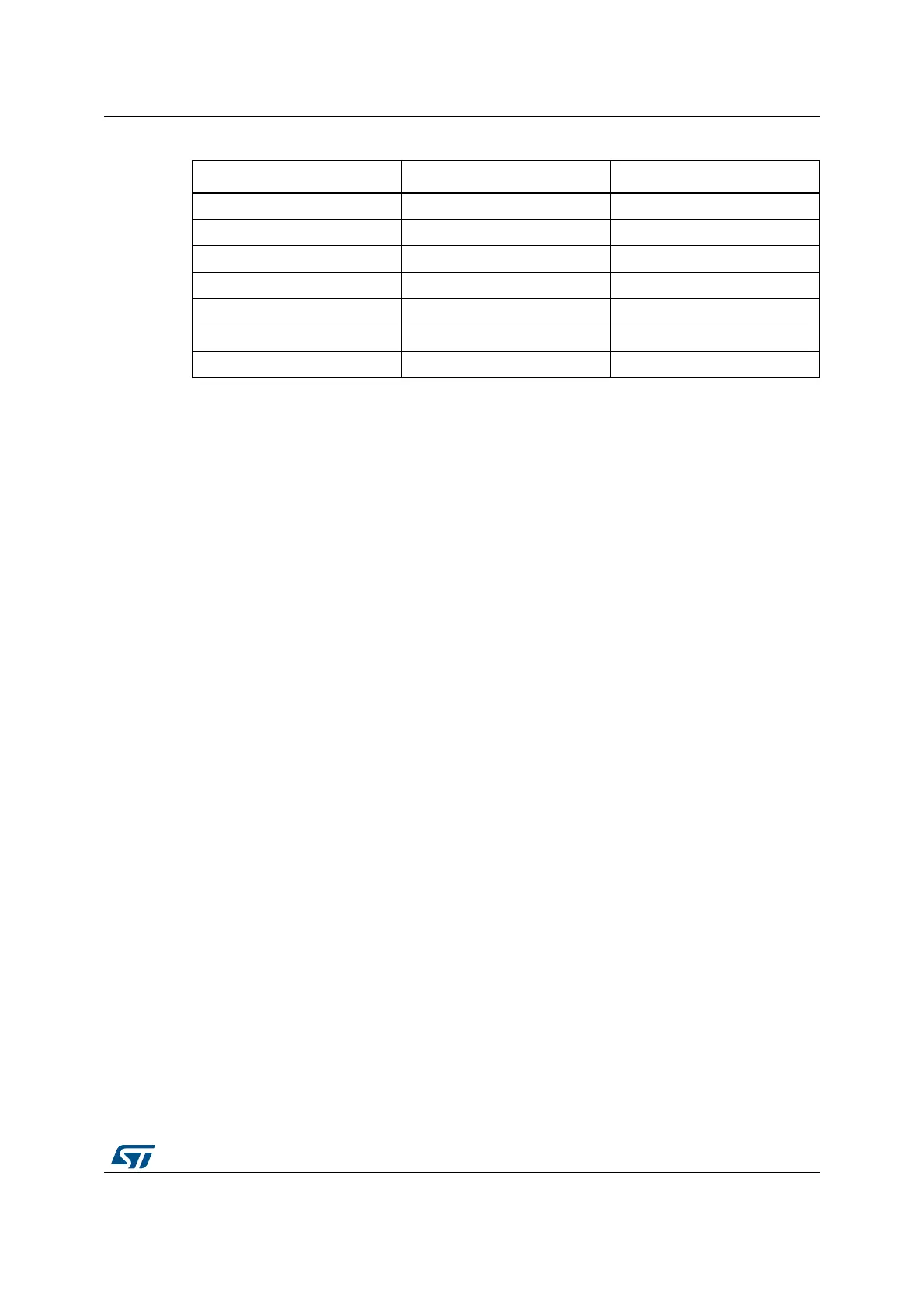

Page 57 0x1000 E400 0x1000 E7FF

Page 58 0x1000 E800 0x1000 EBFF

Page 59 0x1000 EC00 0x1000 EFFF

Page 60 0x1000 F000 0x1000 F3FF

Page 61 0x1000 F400 0x1000 F7FF

Page 62 0x1000 F800 0x1000 FBFF

Page 63 0x1000 FC00 0x1000 FFFF

Table 3. SRAM2 organization (continued)

Page number Start address End address

Loading...

Loading...